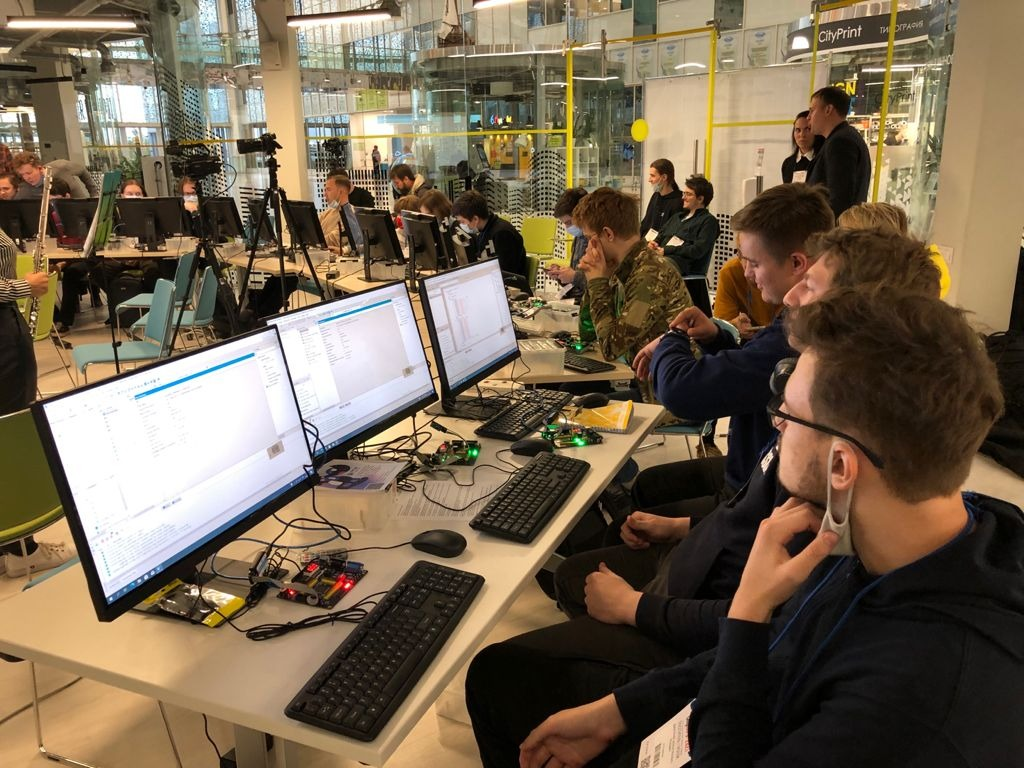

Мы с коллегами из МИЭТ, Ядро / Syntacore, МИРЭА, ВШЭ МИЭМ, МГУ, Иннополиса, ЧНТУ, Самарского университета, Siemens EDA и с поддержкой от Cadence Design Systems - проводим, начиная с 30 октября, курс на 13 суббот под названием "Сколковская Школа Синтеза Цифровых Схем". Это сильно расширенная версия трехдневной школы на ChipEXPO, которая прошла на ура в сентябре.

Суть школы - знакомство с маршрутом проектирования RTL2GDSII, который применяют проектировщики чипов в Apple, Intel итд, используя в качестве тренажера лабы на микросхемах реконфигурируемой логики FPGA, как это делают например в MIT в курсе 6.111. Помимо лаб на FPGA в курсе будет туториал по ASIC flow используя софтвер от Cadence, после которого, если мы договоримся, будет экскурсия на фабрику микросхем в Зеленограде.

Число регистраций снова в несколько раз превысило число посадочных мест в Сколково, поэтому большая часть участников вероятно будет проходить школу удаленно , как и зарегистрировавшиеся вне Москвы, в том числе в Белоруссии, Украине, Азербайджане, Казахстане итд - среди зарегистрировашихся есть даже русские живущие в Германии.

Если в этом посте вы читате про школу в первый раз и хотите зарегистрироваться, то регистрация здесь. Теперь про подготовку.

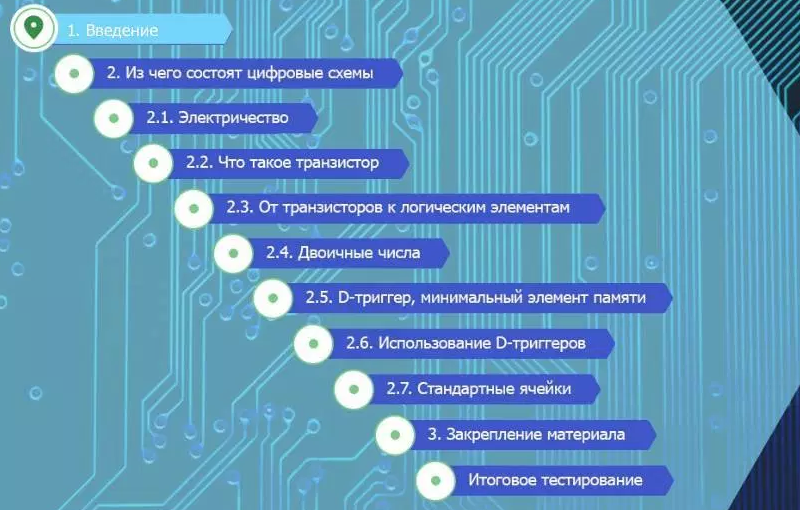

Прежде всего перед школой мы рекомендуем пройти три части онлайн-курса "Как работают создатели умных наночипов" с сайта образовательного отделения РОСНАНО. Во время школы будут возникать концепции, в частности функция D-триггера / последовательностная логика / уровень регистровых передач, которые не сразу укладываются в голову. Онлайн-курс ускорит этот процесс, а также покажет, как упражнения на школе связаны с большой электронной промышленностью. Кроме этого, мы на школе отдает приоритет в посадочных местах и в распределении плат тем, кто прошел этот курс.

Что входит в роснановский курс. Часть 1. От транзистора до микросхемы. В ней то, что вы уже скорее всего знаете из средней школы (уровни напряжения, транзистор, логические элементы и-или-не, двоичные числа), далее то что вы могли слышать, но нужно знать очень четко (D-триггер) и менее знакомый школьникам и студентам младших курсов материал: ASIC standard cell library - стандартные (в смысле "стандартной высоты") ячейки библиотеки примитивов, которые выстраиваются рядами на микросхеме, выпекаемой на фабрике:

Часть 2. Логическая сторона цифровой схемотехники. Тут в основном новый материал: что такое язык описания аппаратуры, как из него синтезируется схема и как в логику попадает физика (временные задержки на логических элементах внутри такта):

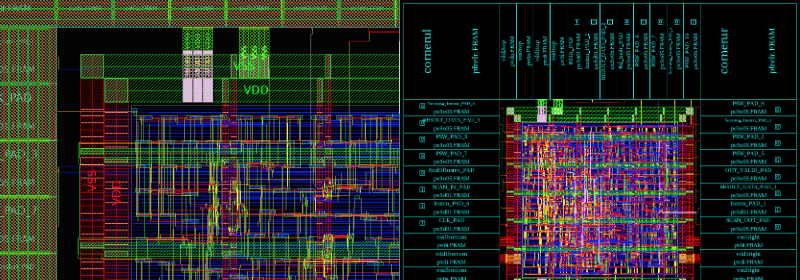

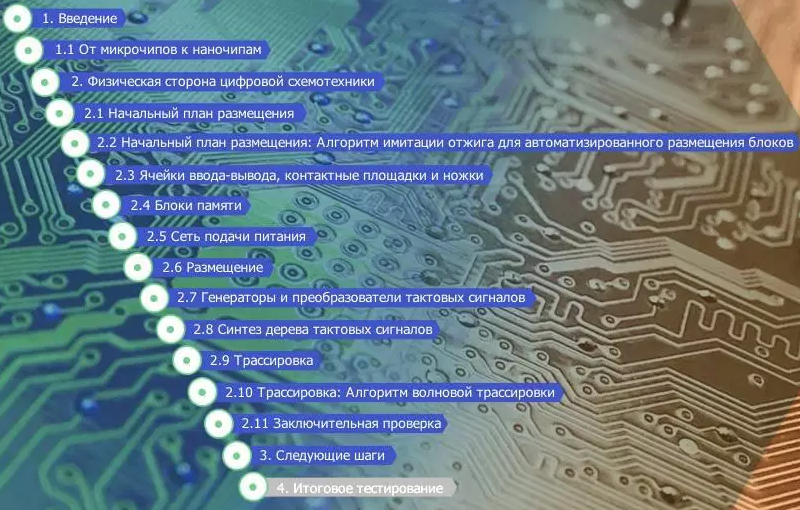

Часть 3. Физическая сторона цифровой схемотехники. Это материал о работе софтвера, который раскладывает граф логической схемы по площадке микросхемы. Такой софтвер для массовых микросхем (например микросхем в смартфонах) может стоить сотни тысяч долларов на инженерное место. Мы дадим вам попробовать такой софтвер на одном из занятий, чтобы вы почувствовали себя на месте такого проектировщика. На остальных занятиях вы будете использовать бесплатный софтвер для FPGA, у которого похожие принципы, но который работает для микросхем реконфигурируемой логики:

После прохождения трех частей курса вы получите сертификаты, которые мы просим вас послать организатору ChipEXPO Александру Биленко info@chipexpo.ru, который распределяет места, и Михаилу Коробкову fpga-systems@yandex.ru, который распределяет платы.

Нужно ли приносить компьютер? Для предыдущей трехдневной школы на ChipEXPO нам предоставил компьютеры МИРЭА. До этого, на летних школах в Зеленограде компьютеры ставил МИЭТ. Но в этот раз мы просим участников приносить свои компьютеры. Главным образом это связано с тем, что мы хотим, чтобы у вас была возможность делать собственные проекты дома, а также чтобы вы умели устанавливать Intel FPGA Quartus и настраивать все сами. Если у вас нет компьютера, или он не подходит, мы предоставим вам один их компьютеров, которые мы планируем купить специально для таких случаев. То есть для 25 посадочных мест мы купим 5-10 компьютеров, расчитывая что все остальные принесут компьютеры сами. Это также позволит купить больше плат для руководителей кружков и преподавателей вузов регионах.

Деньги на компьютеры, платы и сенсоры выделила российская компания Ядро / ее отделение Syntacore, которые проектируют прорывной российский суперскалярный процессор с внеочередным выполнением инструкций, и которые заинтересованы в подготовке будущих разработчиков процессоров.

Какой приносить компьютер? Критическим требованием является то, что на компьютере должна запускаться программа Intel FPGA Quartus Prime Lite Edition v20.1.1.

Для этого требуется Intel/AMD PC с 4-6 GB ОЗУ и 16-20 GB свободного дискового пространства. Некоторые версии Quartus можно запустить и на 2 GB ОЗУ под Linux, где Quartus не так задыхается от нехватки памяти, как под Windows, но это на крайний случай.

Какая операционная система? Quartus 20 официально поддерживается под Windows 10 и несколькими дистрибутивами Linux: Red Hat 7 и 8, CentOS 7.5 и 8.0, SUSE SLE 12 и 15, Ubuntu 16.04 LTS, 18.04 LTS и 20. Юрий Денисов смог запустить Quartus под Astra Linux.

Quartus не работает под Apple MacOS, то есть может работает под виртуальной машиной, но мы не пробовали. Также разные версии Quartus работают под Windows 7, но вам может понадобиться использовать более старую версию, и мы не сможем вам помочь в танцах с бубном вокруг этих версий - то есть это к сожалению между гуглом и вами. Все наши примеры на школе должны идти на версиях Quartus начиная с 13.0sp1, но сейчас мы проверяем только Quartus Prime Lite Edition 20.1.1 под Win10 и Ubuntu / Lubuntu 20.04 LTS.

Какие танцы с бубном нужны для установки Quartus? Увы, они нужны. Текущая бесплатная версия Quartus Prime Lite Edition 20.1.1 не работает сразу после скачивания ни на текущей версии Windows 10, ни на текущей версии Linux Ubuntu 20.04 LTS. Для Windows у нее истекла дата сертификата драйвера, а для Linux она использует устаревшую библиотеку.

Обе проблемы можно решить: для Windows - c помощью скачивания patch, а для Linux - с помощью "sudo ln -sf /lib/x86_64-linux-gnu/libudev.so.1 /lib/x86_64-linux-gnu/libudev.so.0".

Если вы эстет-линуксоид и хотите решить проблему без sudo и установки symbolic link в рутовую директорию /lib, вы можете использовать вот такой скрипт, написаным Алексом Белицем.

В качестве инструкции для установки можно использовать видео Сергея Иванца с прошлого года, но применять их для нового пакета, а также использовать новые версии Quartus для Linux и Windows.

А что по этому поводу думает Интел?

Оказывается, проблемы с бесплатной версией Quartus задевают даже самих сотрудников Интела, до уровня старшего менеджера образовательных программ Ларри Ландиса. Ларри помимо должности в Интеле преподает курс похожий на нашу школу, в Калифорнийском Государственном Университете в Сакраменто. Он мне написал, что для группы, которая разрабатывает Quartus, бесплатная версия не очень приоритетна, и они ее за год так и не исправили. Поэтому Ларри использует более старую версию Quartus 18.1.

Все это очень загадочно, так как для меня очевидно, что большинство пользователей Quartus-а - студенты университетов, и у них явно нет $3995 на платную версию.

Ну что-ж, если даже в Интеле твориться такой бардак, то у российcкого процессора от Yadro / Syntacore больше шансов на мировом рынке, чем многие об этом думают.

Мы очень просим вас установить и запустить Quartus перед тем, как вы прийдете в школу. Преподаватели школы не смогут бросить всех остальных и заняться установкой на ваш компьютер Quartus (это может занять от 20 минут до полутора часов), а также загрузкой патча, проверкой, ту ли версию вы скачали и не требует ли она платной лицензии итд.

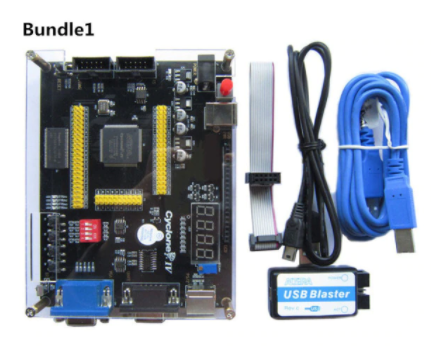

Какие мы используем FPGA платы. Для работы школы мы выбрали минималистические, но при этом достаточные для наших задач платы. В качестве стандартных плат выступают Omdazz и RzRd с ПЛИС Intel FPGA / Altera Cyclone IV. Фактически это одна и та же плата, они отличаются только они отличаются только порядком подключения пинов FPGA к светодиодам (LED) - слева направо или справа налево.

Omdazz и RzRd будут на очной школе + мы выделим некоторое количество плат руководителям кружков и преподавателям вузов в регионах, при условии что они предьявят сертификат с роснановского курса. Однако если вы хотите купить одну из этих плат сами, вот ссылка на Omdazz и ссылка на RzRd - дороже, но с более быстрой доставкой. Вы можете изменить время доставки за дополнительную плату, если кликнете на выпадающий список "доставка".

Мы также используем плату PisWords-6, которая по спецификации лучшая из трех, так как на ней широкий семисегментный индикатор с восемью цифрами, а на Omdazz и RzRd - только на 4 цифры. Кроме этого у PisWords есть раздельные кнопки и переключатели, а у Omdazz и RzRd - совмещенные. Но PisWords только появилась в этом году, и в ней вероятность дефектов может быть больше чем в Omdazz и RzRd. Кроме этого, поставщики PisWords постоянно меняют магазины на AliExpress. Вы можете попробовать ее купить здесь, но не удивляйтесь, если магазин через пару недель вдруг отменит заказ. Кроме этого, она часто продается без USB Blaster, который нужно заказывать отдельно (см. ниже).

При покупке платы Omdazz / RzRd и особенно PisWords-6 важно следить чтобы она шла с USB Blaster. Это компонент для конфигурации платы от PC. Если вы случайно или намеренно купили такую плату без USB Blaster, вы можете или заказать его отдельно на AliExpress, или купить USB Blaster в России (он продается в Москве). Я часто докупаю дополнительные USB Blaster-ы, так как они дешевые и при этом бластеры в комплекте иногда глючат, поэтому хорошо иметь запасной:

У некоторых участников школы уже есть своя плата другого типа. Разберем, какие из них можно применять.

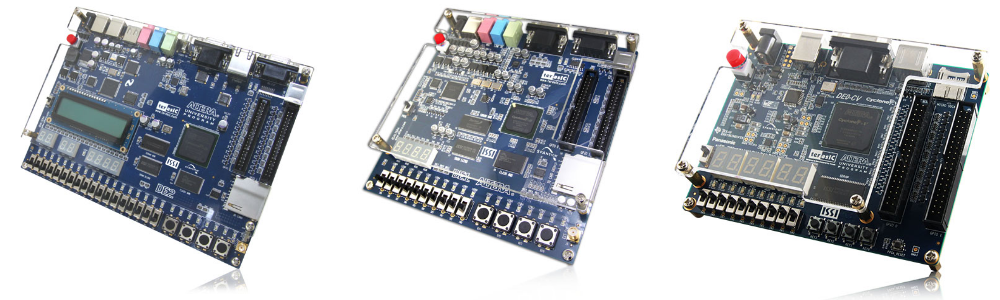

Terasic DE10-Lite с Intel FPGA MAX10. Это хорошая плата, с большим FPGA, который позволяет конфигурировать в ней даже довольно большие промышленные CPU микроконтроллерного класса. Кроме этого у нее удобные переключатели и относительно широкий 7-сегментный индикатор из 6 цифр. На ней также работает много примеров школы, кроме примеров с распознаванием и генерацией звука.

Однако эта плата дороже, а мы стремимся к использованию плат, которые бы могли себе позволить малобюджетные кружки. Кроме этого не Terasic DE10-Lite статический семисегментный индикатор, а у нас есть примеры с динамическим. В общем вы ее можете использовать, если сами спортируете на нее примеры со звуком.

ZEOWAA. Неплохая, очень недорогая плата, с тем же Intel FPGA / Altera Cyclone IV, что и Omdazz, но без внешней микросхемы памяти. На этой плате идут большинство примеров школы, кроме примеров со звуком и примеров с продвинутой микроархитектурой (они будут с января). К сожалению эту плату больше нельзя купить на AliExpress.

Также у зарегистрировавшихся участников есть другие альтеровские платы - Terasic DE2, DE2-115, DE0, DE0-CV, Марсоход итд. Многие из них годятся для упражнений, но в пакете примеров школы у нас нет для них wrapper-а. Под этим словом я подразумеваю три файла:

top.v - код на верилоге, модуль верхнего уровня, порты которого соответствуют пинам ПЛИС, которые соединяются с внешними сигналами: генератором тактовой частоты, сбросом, кнопками, светодиодами, VGA итд.

top.qsf - файл установок, фактически код на языке Tcl для программы синтеза Quartus, который задает: модель ПЛИС, имена используемых файлов на верилоге, соотвествие портов модуля на верилоге пинам ПЛИС, а также параметры пинов.

top.sdc - другой файл установок, тоже код на языке Tcl для программы синтеза Quartus, который задает тайминг: максимальную частоту тактового сигнала, а также пины, для которых привязку к тактовому сигналу программа синтеза может игнорировать.

Если вы хотите, вы можете сделать эти wrapper-ы сами, используя в качестве примеров файлы отсюда. Также замечу, что для некоторых плат, в частности DE2 (но не DE2-115) вам понадобится старая версия квартуса.

"А зачем эти файлы? Давайте сгенерим их во время школы в GUI квартуса, как показывается в некоторых альтеровских туториалах".

Нет, не стоит, это неэффективное использование времени школы. Мы пытаемся научить будущих микроархитекторов ASIC-ов, и лучше потратить время на эффективное писание кода на верилоге и разбор конвейерных микроархитектур, чем на механическую вождение мышкой по GUI квартуса.

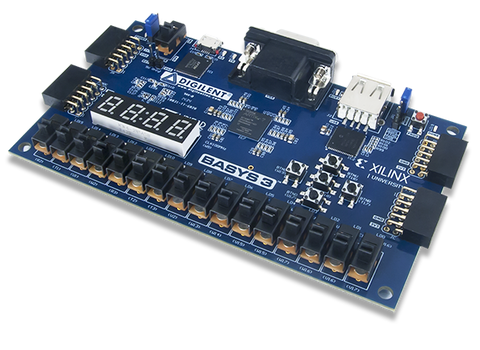

"У меня плата с Xilinx. Помогите мне запустить на ней примеры". Хотя при желании все примеры можно запустить на платах с Xilinx Spartan-6, Spartan-7, Artix-7 и даже Spartan-3E, но у нас не хватает времени на школе, чтобы показывать и систему разработки от Intel FPGA / Altera, и систему разработки от Xilinx: ISE и Vivado.

И опять же, детали синтеза для Xilinx не помогает изучению микроархитектуры, где вся интеллектуальная соль проектирования ASIC чипов для смартфонов и самоуправляющихся авто.

Кроме этого, платы с Xilinx FPGA дороже для малобюджетных кружков, поэтому мы выбрали Intel FPGA / Altera.

При этом вы можете сами спортировать примеры для Xilinx, используя файлы установок для плат Digilent Basys3 и Nexys4.

А можно ли использовать платы, которые втыкаются в макетную? Можно, если вы сами напишете врапперы примеров и купите для них VGA коннектор для примеров с VGA:

А как насчет плат от Lattice и MIcrochip / Microsemi? Они реже применяются, имеют проблемы с поддержкой верилога, поэтому мы их не используем. Впрочем, вы можете поэкспериментировать с Lattice, у которого, говорят, есть open-source toolchain.

А как насчет ПЛИС российского производства из Воронежа? - слишком дорогие и непонятной доступности. Видимо пока не для массового обучения российских студентов и школьников.

Для проверки, что ваша FPGA плата и установка Quartus работает, вы можете скачать минимальный пакет "before" по следующей ссылке:

ChipEXPO 2021 Digital Design School before package v2.0 https://bit.ly/chipexpo2021ddsbefore20

Прямая ссылка

Вот видео от Сергея Иванца, как запустить пример из этого пакета:

Вы также можете, если очень хотите, попробовать Quartus в режиме рисования схем мышкой. В промышленности это не применяется с начала 1990-х годов, вместо этого разработчики вводят код на Verilog или VHDL и смотрят, какая схема их этого получилась

Но некоторые преподаватели вузов делают первое занятие таким образом, чтобы студенты четко понимали, что даже когда они пишут код на верилоге, они фактически рисуют на нем схему, а не пишут программу (цепочку инструкций для процессора).

Вот видео от Сергея Иванца с таким туториалом:

С Quartus, платами и их проверкой мы закончили. Теперь перейдем к оборудованию, которое может вам понадобиться на последующих занятиях. Мы постараемся им снабдить всех очных участников, а также заочных преподавателей, но если кто хочет закупить его для себя, то необходимая информация ниже.

Для упражнений с графикой вам понадобится дополнительный VGA монитор, который подключается к FPGA плате. Я предпочитаю портабильный монитор (для может понадобиться дополнительный кабель), но в принципе почти любой монитор с VGA входом подойдет. Вот пара видео тоже от Сергея Иванца как делать лабы с графикой:

Если вы хотите развить пример игры, то вы можете приобрести SPI джойстик, мы покажем как подключить его к схеме в FPGA плате. Вот пример такого джойстика от компании Digilent, правда его там может быть нетривиально заказать (см. инфо ниже про лабы с музыкой).

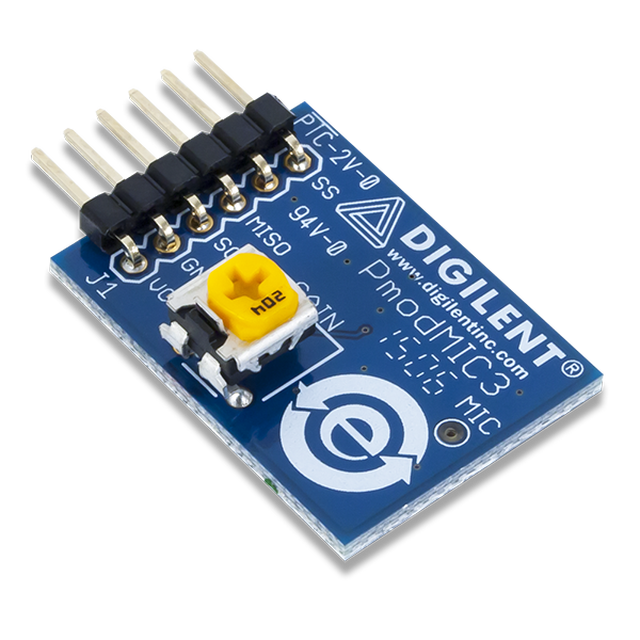

Для лаб с генерацией и распознаванием музыкальных мелодий понадобится микрофон c SPI интерфейсом и усилитель с I2S интерфейсом, а также простые наушники с круглым входом. Микрофон и усилитель мы заказываем в компании Digilent. Мы опять же собираемся снабдить этими компонентами всех участников офлайн, но если вы хотите их купить сами, то тут есть тонкий риск: в ~2012-2013 годах Digilent доставлял в Россию без проблем, но потом они ввели сложные правила для продажи через российского дистрибутора, а прямые продажи с сайта убрали. Сейчас они снова поставили продажи в Россию обратно на сайт, но если они посылают в Россию через UPS (не путать с USPS) или с FedEx, то это будет нелегко растаможить (таможня требует кучу бумаг). Чтобы таможня ничего не требовала, нужно слать через банальную государственную почту USPS (US Postal Service), у которой специальное соглашение с Почтой России через международный кооператив EMS.

Короче, можете заказывать на свой страх и риск. Вот микрофон и код на верилоге, который принимает от него данные. В худшем случае компоненты вернутся обратно в штат Вашингтон и Digilent вернет за них деньги.

А вот усилитель и соответствующий код примера. В него втыкаются обычные наушники с круглым штырем, но если вы хотите генерить стерео-звук, то нужны или наушники с двумя штырями (такие раздают в самолетах) или вот такой сплиттер.

Распознавание мелодий с флейтисткой Марией Беличенко на ChipEXPO выглядело так:

Если вы хотите сами поиграть на флейте перед FPGA платой (или скажем объединить это с графикой на VGA и сделать скажем танцующих на экране кобр), вы можете купить блокфлейту (на ней гораздо проще играть новичку, чем на поперечной флейте Бема, на которой играет Мария на видео), и Мария, которая будет в Москве на этом занятии школы, поучит вас сыграть какую-нибудь простую мелодию:

Другие полезные периферийные устройства, которые вы можете использовать для проектов с FPGA платой во время нашей школы:

Поворотный энкодер, Digilent Pmod ENC: Rotary Encoder

Датчик освещения, Digilent Pmod ALS: Ambient Light Sensor

Ультразвуковой измеритель расстояния

Матрица кнопок

И более навороченная матрица кнопок

С сенсорами закончили. Теперь во время работы школы вам может быть полезной литература. В первую очередь это теоретическая книжка Харрис & Харрис, на которую мы будем много раз ссылаться. К ней есть версия для планшета и более короткие слайды для лекций.

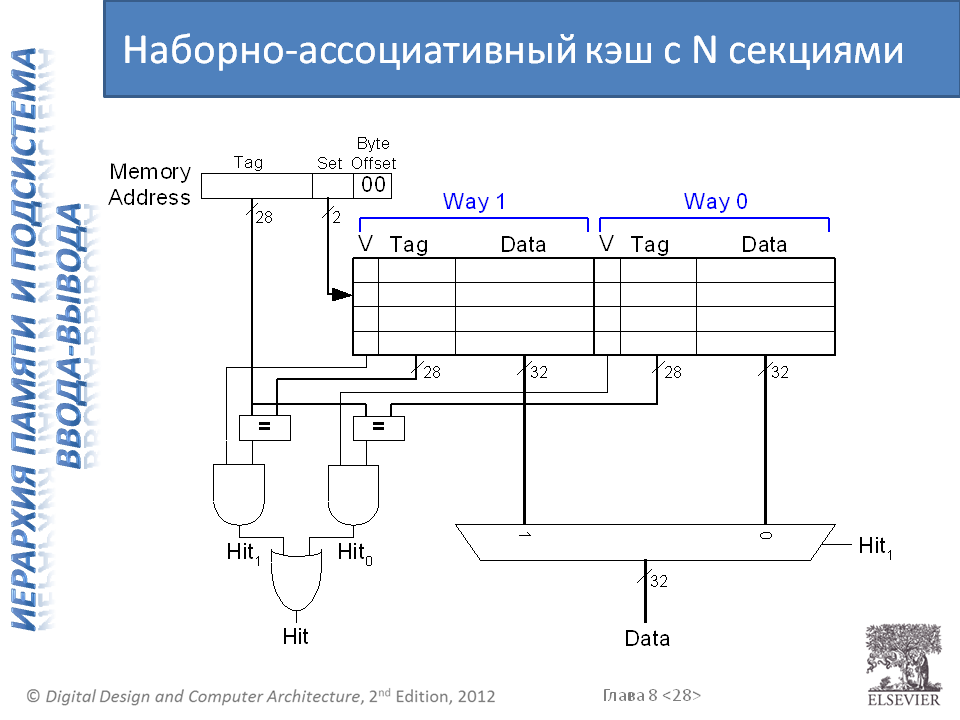

Харрис & Харрис начинается с нуля и доходит до довольно продвинутого материала, который мы будем использовать в конце курса, когда будем создавать процессорный кэш:

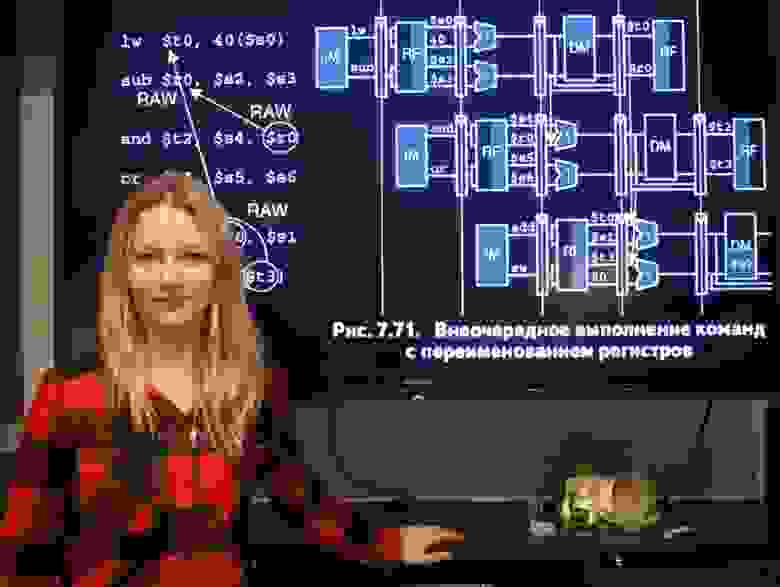

В Х&Х есть даже чуть-чуть про процессоры с суперскалярным конвейером с внеочередным выполнением инструкций и переименованием регистров - это та самая тема, на которую сейчас российское правительство финансирует прорыв:

За переводной книжкой Харрис & Харрис идет написанный российскими и украинскими авторами лабник "Цифровой синтез". Как нетрудно догадаться, то те же авторы, которые проводят и лекции и семинары на Сколковской Школе Цифрового Синтеза:

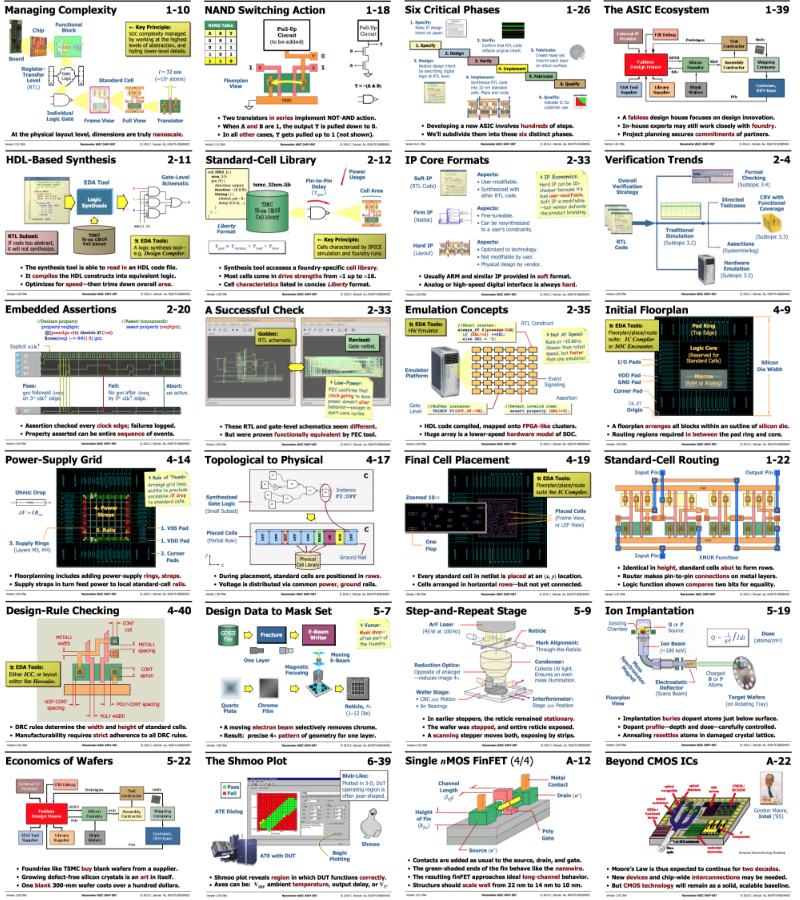

Ближе к зиме мы будем проводить туториал по маршруту проектирования ASIC-ов. Это фиксированные микросхемы, которые выпускаются на фабриках миллионами и миллиардами и стоят в гаджетах. К тому времени участникам школы может быть полезно скачать и полистать русский перевод слайдов Чарльза Данчека к лекциям, которые Чарльз читал сначала в Университете Калифорнии Санта-Круз, расширении в Silicon Valley, а потом в 2016 году прочитал в Москве, Санкт-Петербурге и Киеве:

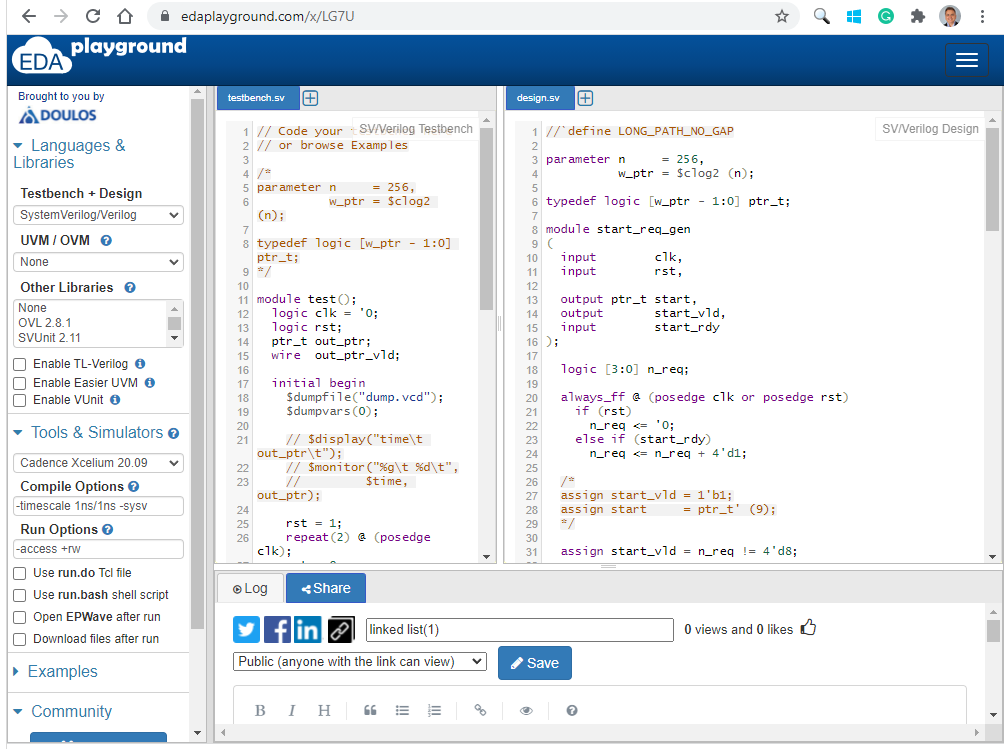

С книгами пока все. Еще во время школы крайне желательно для всех участников зарегистрироваться на вебсайте EDA Playground. Для регистрации этот сайт требует официального емейла университета или компании, но зато после регистрации он позволяет доступ к дорогим профессиональным симуляторам, которые поддерживают SystemVerilog - крупное расширение верилога. Это будет очень полезно, когда мы перейдем к более продвинутой микроархитектуре после Нового Года.

Харрис & Харрис может быть вам полезен уже во время первого занятия, как и EDA Playground. Большинство участников во время первого занятия будут пробовать простые упражнения, под руководством Александра Силантьева из МИЭТ и его коллег из МИРЭА и других вузов. Эти упражнения более-менее самодостаточны. Но некоторые из участников прийдут на первое занятие, уже зная основы верилога. Что с ними делать?

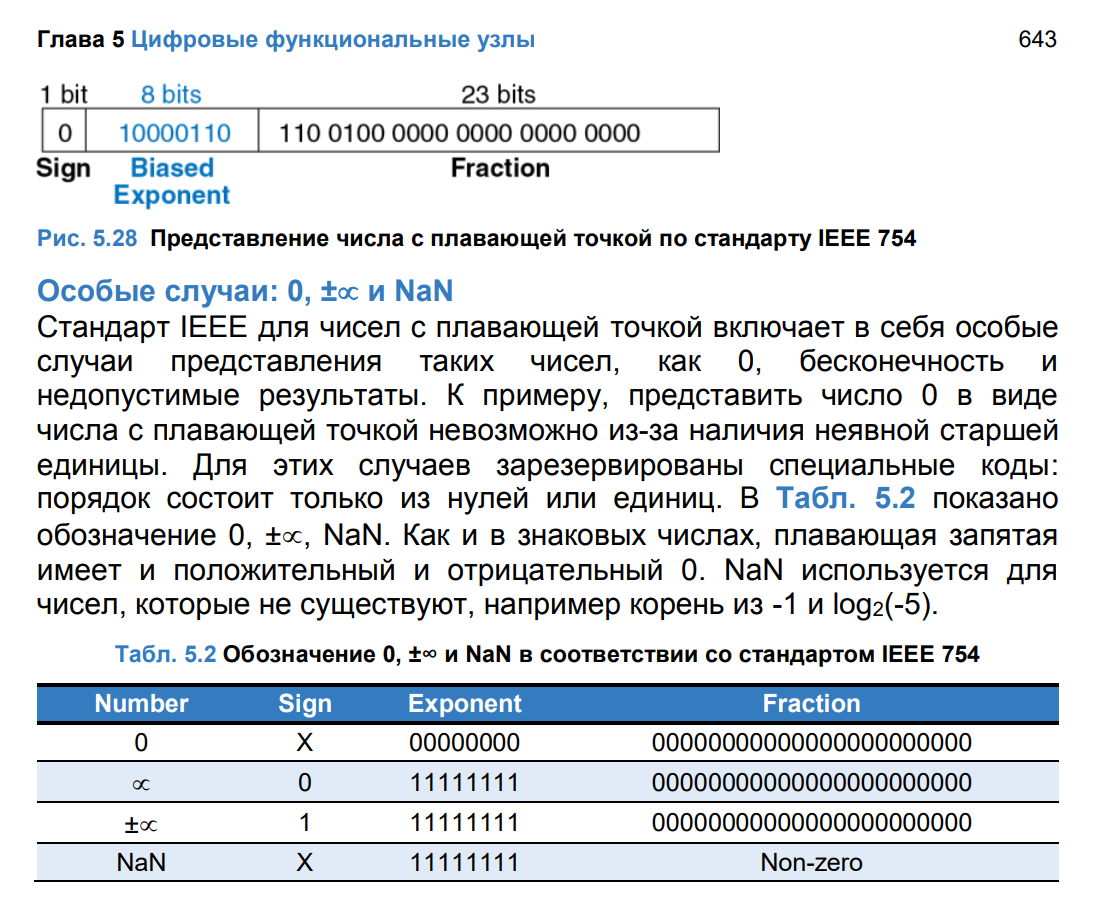

Чтобы никто не скучал, мы договорились с Ильей Кудрявцевым (на снимке справа), деканом из Самарского Университета (бывшего Самарского Аэро-Космического), что он прочитает вам короткую лекцию про операции с числами с плавающей точкой. После чего скучающие участники реализуют комбинационный IEEE 754 сумматор с детекцией положительной и отрицательной бесконечностей, а также NaN (вы узнаете что это такое). Илья подготовит для вас слайды с форматом и алгоритмом, а также сделает обзор операций языка (детали переполнения при сложении и вычитании, конкатенация и выделение группы битов) и нужных для комбинационной логики конструкций (assign, wire, always @*, if), а также обсудит верификацию такого блока.

Про плавающую точку написано аккурат в Харрис & Харрис:

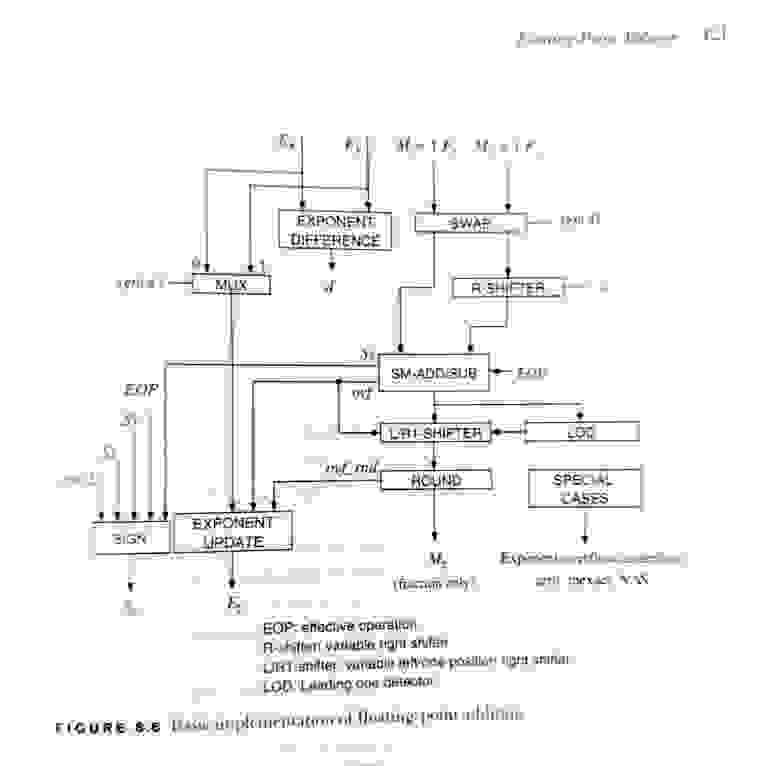

Картинка реализации из книжки Digital Arithmetic by Miloš D. Ercegovac and Tomás Lang:

А зачем вам EDA Playground? В нем поддерживается SystemVerilog, а в нем есть удобная для верификации функция преобразования несинтезируемого числа с плавающей точкой в биты и наоборот: $bitstoreal / $realtobits для 64-битных чисел и $bitstoshortreal / $shortrealtobits для 32-битных.

Вся эта арифметика не настолько скучная, как поначалу кажется. Ведь графические процессоры, которые рендерят игры с монстрами, набиты этими сумматорами и умножителями с плавающей точкой - они используются для быстрого преобразования координат треугольников, из которых эти монстры состоят.

Так что до встречи на первом занятии Сколковской Школы Цифрового Синтеза 30 октября! (О времени и месте вам сообщат по емейлу регистрации)