Прежде чем перейти к статье, хочу вам представить, экономическую онлайн игру Brave Knights, в которой вы можете играть и зарабатывать. Регистируйтесь, играйте и зарабатывайте!

Согласно статье Ивана Покровского "Возможности и проблемы отечественной микроэлектроники", в России всего две тысячи разработчиков микросхем. Для сравнения: в каждой крупной международной электронной компании есть несколько команд, работающих над чипом или над IP, в каждой по паре сотен разработчиков (хотя бывает и меньше ста, и больше тысячи).

Две тысячи человек - это мало для любого сценария развитии России:

1. Как для сценария, в котором санкции будут сняты и российские компании будут беспроблемно работать с TSMC и западными партнерами для разработки маркетируемых на мировом рынке чипов.

2. Так и для сценария, в котором российские разработчики будут строить экосистему проектирования в условиях изоляции, ориентироваться на производство микроконтроллеров и встроенных микросхем на зеленоградском Микроне, а также на сотрудничество в разработке semiconductor IP с китайскими производителями.

В других стран бывшего СССР ситуация еще хуже.

Что же делать? Для ответа на этот вопрос мы привлекли Машу Горчичко - выпускницу МИФИ, которая защитила диссертацию в Университете Вандербильда в Теннесси. Маша работала инженером в Роскосмосе, а сейчас работает в Кремниевой Долине, разработчиком в компании Applied Materials - одного из лидеров в оборудовании для производства микросхем.

Представим Машу, которая будет пояснять и иллюстрировать наши тезисы на видео. От себя прибавлю, что МИФИ - крутой вуз, в нем внутри есть ядерный реактор, а на входе стоит автоматчик:

Также, если вы посмотрите на Машин linkedin, вы можете увидеть, что она получила сертификат окончания школы по управлению спутниками, а также спроектировала I2C контроллер на верилоге для ПЛИС в Роскосмосе.

Да, но вернемся к 2000 российcким инженерам. Собственно что делать, понятно: нужно привлекать в отрасль больше молодежи, начиная со школьников. Чтобы к моменту поступления в вуз они уже представляли возможность развития своей карьеры в проектировании микросхем, на втором курсе писали бы на SystemVerilog на уровне регистровых передач, на третьем осваивали бы технологии верификации, на четвертом - физическое проектирование, на пятом - продвинутую микроархитектуру.

Альтернативы такому подходу нет. Если начинать привозить разработчиков из Калифорнии, Тайваня, Великобритании, Индии и других таких мест, то возникнет вот какая проблема: большинство разработчиков - люди узкоспециализированные, и если набрать винегрет инженеров и ученых на разные темы, которых объединяет лишь желание получить много денег от россиян, то они через пару лет разъедутся обратно и каши за это время не сварят.

При этом привлечение и обучение молодежи - это комплексная задача, и в этой заметке мы затронем только самое начало ее решения: увеличение воронки входа.

Фундаментальная проблема заключается в том, что перед проектированием процессоров и прототипированием их на ПЛИС студенту приходится хорошо повозиться с упражнениями по скурпулезной перестановке битов между тактами, а для таких упражнений не у всех есть мотивация. Но эти упражнения можно сделать более интересными, если превратить их в игру с графикой:

Прежде чем продолжить с ПЛИС - что такое проектирование цифровых микросхем вообще? 50 лет назад инженеры рисовали вручную на бумаге дорожки и транзисторы, 40 лет назад возили мышкой по экрану, расставляя логические элементы, но 30 лет назад произошла революция так называемого логического синтеза. После нее мейнстримом стало проектирование цифровой части микросхем с помощью кода. Но не кода программы для запуска ее на процессоре, а коде на языке описания аппаратуры (Verilog или VHDL), который можно превратить в сам процессор:

Теперь что же такое ПЛИС. Это своего рода кубики лего для проектировщика. Микросхема, которая состоит из ячеек с изменяемой логической функцией. Причем изменяемой не на фабрике, а у вас на столе. Записываете одну последовательность бит в память конфигурации - ячейка стала логическим элементом И, записываете другую - она стала D-триггером:

Теперь как выглядит один из примеров графики на ПЛИС:

Но это динамический пример, в котором изображение движется. Начинать лучше со статического примера, в котором школьник просто пишет на верилоге комбинационный код (то есть код без элементов состояния), который вычисляет цвет в зависимости от координат на экране. Координаты x и y, как и сигналы для генерации развертки, выходят из уже написанного модуля vga в пакете упражнений. Если к нему добавить например вот такой код, то на экране появится парабола с цветовым переходом:

wire [Y_WIDTH * 2 - 1:0] x_2 = x * x;

always_comb

begin

red = '0;

green = '0;

blue = '0;

if (display_on & x_2 [9 +: Y_WIDTH] < y)

begin

red = x [X_WIDTH - 2 -: 4];

green = y [Y_WIDTH - 2 -: 4];

blue = '1;

end

end

Этот код превращается не в программу (последовательность команд процессора, как в Ардуино), а в граф из логических ячеек, по которому конфигурируют ПЛИС:

Пример же, который показывает Маша на видео, требует дополнительных элементов последовательностной логики, а именно счетчиков, которые меняет свое значение со временем, на основе тактового сигнала с частотой 50 MHz. Этот код выглядит так (см. по ссылке Pattern 2):

Сначала, на каждом положительном фронте (переходе из 0 в 1) тактового сигнала мы увеличиваем значение 23-битного счетчика cnt:

logic [22:0] cnt;

always_ff @ (posedge clk)

if (rst)

cnt <= '0;

else

cnt <= cnt + 1'd1;Счетчик - это по сути комбинация из сумматора и D-триггеров, которая работает так:

Затем на основе счетчика мы генерируем сигнал enable, пульс, который возникает на 1 такт шесть раз в секунду: 50 MHz / 2 в степени 23 = 6 Герц:

wire enable = (cnt == '0);Теперь мы заводим два 8-битных счетчика, dx и dy, которые будут увеличиваться в зависимости от того, нажимаем ли мы или не нажимаем две кнопки.

Кнопки используют негативную логику. Если кнопка не нажата, то с нее приходит 1, а если нажата - 0. Так как мы используем еще и сигнал enable, сгенерированный от счетчика cnt, наших два новых счетчика будут увеличиваться максимум на 6 за секунду:

logic [7:0] dx, dy;

always_ff @ (posedge clk)

if (rst) // сигнал сброса

begin

dx <= 4'b0;

dy <= 4'b0;

end

else if (enable) // это условие срабатывает 6 раз в секунду

begin

dx <= dx + key [2]; // Если кнопка 2 не нажата, увеличиваем dx на 1

dy <= dy + key [1]; // Если кнопка 1 не нажата, увеличиваем dy на 1

endТеперь прибавляем эти счетчики к координатам при вычислении цветов и получаем движущийся узор:

wire [3:0] xc = x [X_WIDTH - 2 -: 4];

wire [3:0] yc = y [Y_WIDTH - 2 -: 4];

always_comb

begin

red = '0;

green = '0;

blue = '0;

if (display_on)

begin

red = xc + xc + yc + dx;

green = xc - yc - dy;

blue = { 4 { ~ key [0] } };

end

end

В ПЛИС, который показан на видео, Intel FPGA / Altera Max II - всего 240 реконфигурируемых логических ячеек. Это очень мало, по сравнению с количеством ячеек ПЛИС на типичных студенческих платах (десятки тысяч) и особенно ПЛИС которые используются для прототипирования промышленных процессоров (миллионы). Например в AMD Xilinx Virtex UltraScale+ VU19P FPGA - 9 миллионов ячеек. Но даже UltraScale+ ПЛИС меркнет по сравнению с фиксированными микросхемами ASIC, в которых могут быть миллиарды транзисторов, что соответствует сотням миллионов cтандартных ячеек ASIC (ASIC standard cell), что соответствует десяткам миллионов ячеек ПЛИС. Именно такие микросхемы стоят в смартфонах и автопилотах автомобилей.

Но для самого начального обучения малое количество ячеек - это лучше, чем большое, так как оно позволяет вырастить интуицию, какие конструкции в верилоге "тяжелые", а какие "легкие" (или "дорогие" / "дешевые" в смысле ресурсов). Например генерация одной параболы (схема первого примера) в ПЛИС влазит, а вот генерация двух - нет. Потому что для параболы требуется операция умножения, а она "тяжелая".

С другой стороны, пример с движущимся квадратным "ковром" занимает всего треть ПЛИС-а, потому что операции сложений, которые в нем используются - "легкие". Правда в примере с ковром много ячеек уходит на биты состояния (D-триггеры) для счетчиков.

Можно устроить соревнование среди школьников, кто сделает самый красивый узор (или самую интересную игру типа пин-понг) используя ограниченное количество ячеек ПЛИС (или несколько соединенных плат). Вся информация где купить платы есть в README.md репозитория проекта Пайка, ПЛИС и Линукс (Исходники, презентации, задания и примеры для летнего лагеря по пайке, микросхемам ПЛИС и синтезу цифровых схем из кода на верилоге под Линуксом).

Хотя пакет работает и под Linux, и под Windows, мы рекомендуем учить школьников под Linux. По банальной причине: все разработчики микросхем, даже в хардверных отделениях Microsoft и Apple, делают синтез и моделирование под Линуксом. Просто потому что разработчики используют программы Synopsys Design Compiler и Cadence Genus + Innovus, и у этих продуктов нет версий ни под Windows, ни под Макинтошем, только под Linux.

Я проверил, что Intel FPGA Quartus с пакетом fpga-soldering-camp работает под несколькими российскими дистрибутивами Linux, включая:

ALT Linux Образование

Simply Linux

Astra Linux

Ред ОС

ROSA Linux

Green Linux

Все их можно применять на летних лагерях школьников.

Мы уже опробовали летние школы с ПЛИС на Летней Школе Юных Программистов в Новосибирске и на школе в МИЭТ в Зеленограде. Правда и в одном и в другом случае были тщательно отобранные школьники.

Что же школьник может делать после такой школы? Они может выбрать путь стать проектировщиком микросхем и пойти учиться в МИЭТ, МИЭМ, МИРЭА или ИТМО, или решить стать прикладным математиком в области алгоритмов автоматизации проектирования и пойти на ВМК МГУ. Или использовать эти знания для специализации в проектировании систем (system design) из процессоров, GPU, ПЛИС, специализированных чипов и софтвера. Хорошая следущая ступенька - это Школа Синтеза Цифровых Схем, которая только в прошлую субботу выдала дипломы 92 участникам. В альбоме участники 11 площадок Школы: ИНБРЭС, Иннополис, ИТМО, МИРЭА, МИЭМ, МИЭТ, НГТУ, Самара, СибГУТИ, УрФУ, ЯДРО:

Те из них кто прошел или пройдет экзамен, описанный в заметке на Хабре "Хотите проектировать устройство, которое использует миллиард человек — решайте микроархитектурные задачки" - получит рекомендации в ведущие электронные компании.

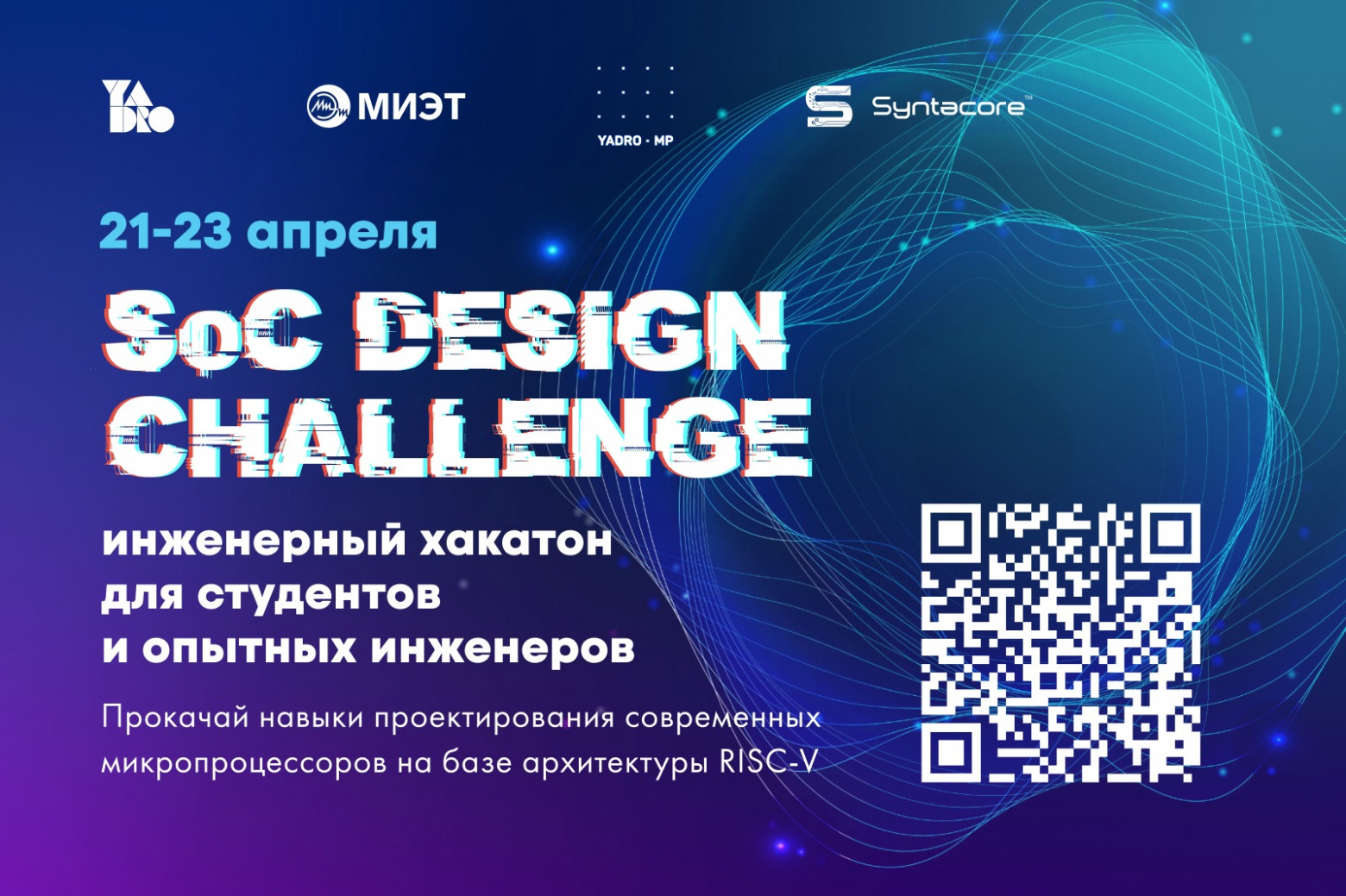

Как сиквел для Школы Синтеза через неделю в МИЭТ будет хакатон по процессорам:

Да, но что же дальше для школьного этапа и летних школ? Во-первых, чисто чтобы начать движуху, мы с моим приятелем Сергеем Рыжковым, основателем интернет-провайдера RiNet - готовы выделить начальные 100 тысяч рублей для поддержки такого рода летних школ. Эти платки по 240 логических ячеек вместе с коннекторами стоят всего около 2000 рублей на школьника, так что этого уже должно хватить для скажем школы в Новосибирске, если они захотят местными силами этим заняться, и еще 3-4 школ.

Во-вторых, если есть интерес у преподавателей кружков, летних школ и центров для школьников, мы с Машей можем записать более подробные видео с инструкциями. Что вы думаете?