Прежде чем перейти к статье, хочу вам представить, экономическую онлайн игру Brave Knights, в которой вы можете играть и зарабатывать. Регистируйтесь, играйте и зарабатывайте!

Как же разработать свою сикросхему. Задался я этим вопросом, когда я захотел создать собственный процессор. Пошёл я гуглить и ничего годного не нашёл. Ответы в основном два։ "Ты не сделаешь свой процессор, потому что слишком сложно" и "Забей и собери компьютер из комлектующих".

Очевидно что это меня не устаивает, поэтому я решил изучить вопрос серьезнее. Оказалось можно сделать свой процессор описав его с помощью Verilog и FPGA. Купил плату в китае, 3 года спокойным теспами написал свой процессор, оттестировал, скомпилировал и залил на FPGA. Но мне этого не достаточно.

Так как же разработать микросхему?

Давайте сначала разберёмся из чего состоит микросхема. Все микросхемы состоят из кремния и корпуса.

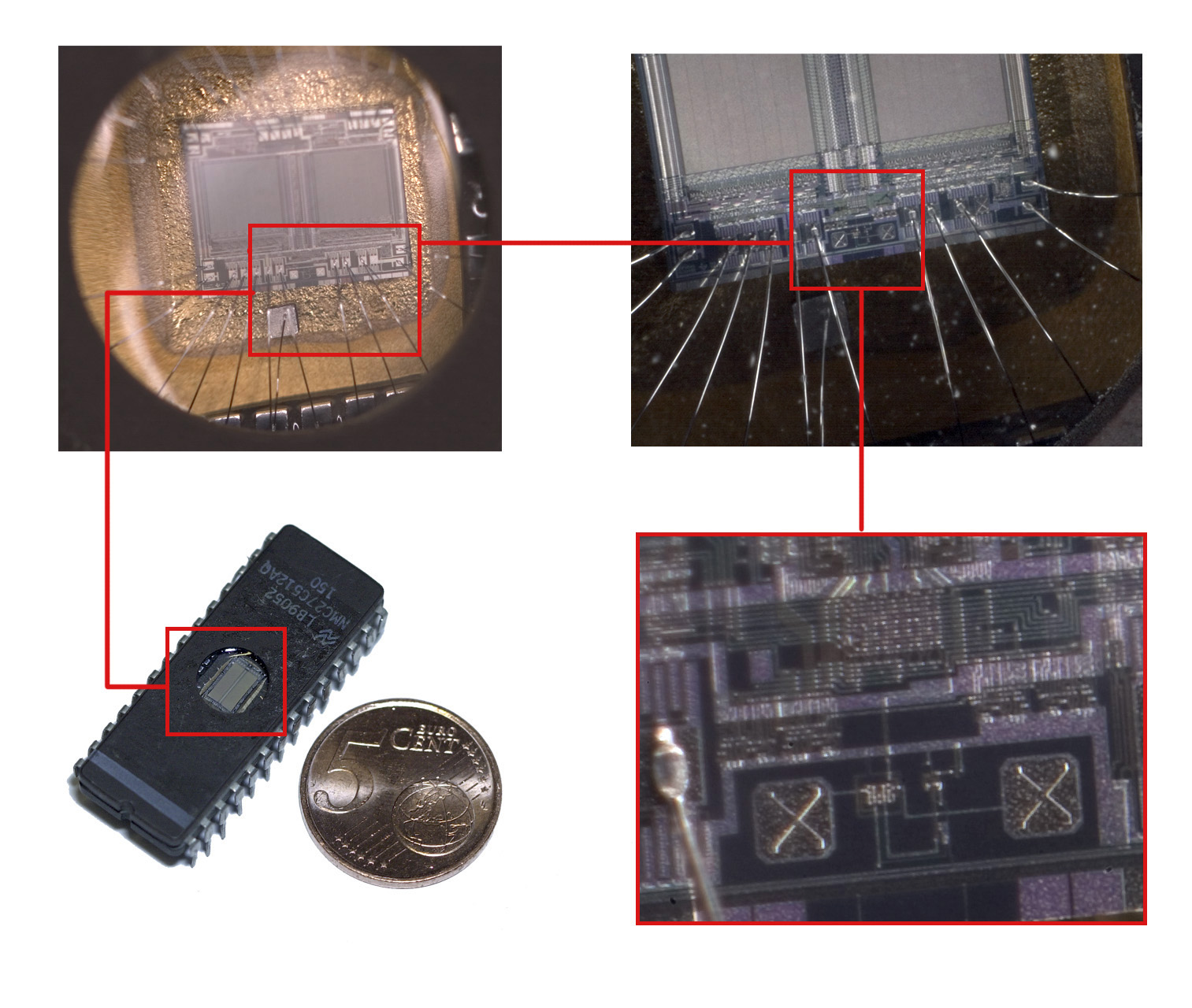

Корпус это кусок пластика и несколько проводов к выводам корпуса. А есть еще силикон. Корпуса микросхем имеют миллион варинтов корпусировки и к этому мы даже не будем подходить. Существует два варианта расположения кристала. Вверх металлом и вниз металлом. На картинке изображены микросхемы вверх металлом. Вниз металлом имеет преимущество ибо не надо провода проводить.

А как же силикон

Силикон производиться на заводе. Каждый завод имеет свою технологию производства. Мы будем расматривать только технологии 250нм-14нм ибо про них я знаю достаточно много.

Для того, что бы производитель произвёл вашу микросхему вам нужно предоставить им GDS-II файл, который являеться грубо говоря векторной многослойной картинкой вашей микросхемы.

Первым шагом к разработке являеться։ связаться с производителем. Если у вас меньше чем 10000 баксов, забудьте. Лучше расмотреть Multi project wafer service [ https://en.wikipedia.org/wiki/Multi-project_wafer_service ].

Не все GDS-II файлы могут произведенны. Для того, что бы понять что можно произвести, а что нет вам понадобиться несколько файлов.

GDS-II файл и так называемый Process Development Kit

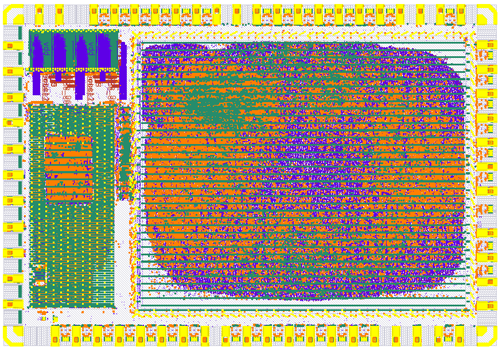

На картинке вы можете видеть интегральную схему SHA3. Большая область справа это и есть SHA3 схема, а всё остальное так называемый Caravel Harness. Для того что бы гугл смог произвести вашу микросхему по технологии SKY130 гугл требует что бы ваша основаня схема помещалась справа и подключаеться к жёлтым точкам. Посмотреть на структуру Caravel Harness можно тут - https://github.com/efabless/caravel/tree/master.

Process Development Kit (https://en.wikipedia.org/wiki/Process_design_kit) эта такая кучка файлов которая содержит։

Технологическая документация.

Этот файл содержит на удобно перевариваемом формате описание и требования к конечному файлу, кроме того эта документация содержит примеры и описания транзисторов.

Модели для симуляции элементов схемы в формате SPICE.

Эти модели импользуеться для симуляции компонентов интегральной схемы. Перед тем как нарисовать схему силикона, вам нужно сначала определиться со схемой, которуя вы будете рисовать.

Технологические файлы, который повзоляют связать файл GDS-II и слои при производстве.

Библиотека примитивов - Транзисторов, резисторов, конденсаторов и так далее

Параметры

Модели для симуляции

Символы для рисования схемы

Правила Design Rule Check

Эти файлы привязанны к конкретному программному обеспеченью и содержат список правил, на которые в автоматическом режиме будут проверятсья ваши интегральные схемы или её отдельнгые компоненты.

Primitive Extraction rules или правила описывающие примитивы. Эти правила позволяют превратить ваш GDS-II представление в список примтивов и иъ связи (netlist). Сгенерированный netlist так же содержит паразитические конденсаторы и резисторы, а сам netlist используеться для того что бы произвести симуляцию компонентов как можно приближежённой к реальной интегральной схеме.

Layout versus Schematic check или правила, которые позволяют получить из вашего GDS-II так называемый netlist, после чего его его можно сравнить со схемой, которую вы нарисовали и уже просимулировали.

Например установщик для технологии SKY130 (130нм) можно найти вот тут http://www.opencircuitdesign.com/open_pdks/install.html. Эти скрипты автоматически установят всё необходимое, но не спешитье ниже мы найдём скрипт, который сделает все за нас.

Иногда производитель силикона так же предоставляет так называемые файлы Standard Cell Library. Эти файлы предоставляют описание отдельных компонентов, который разработчик может использовать для разработки цифровых интегральных съем или её частей. К этому чуть позже.

Здесь стоит оставновиться и понять, из чего конкретно состоит сам силикон.

Как рисовать тразистор и как он работает

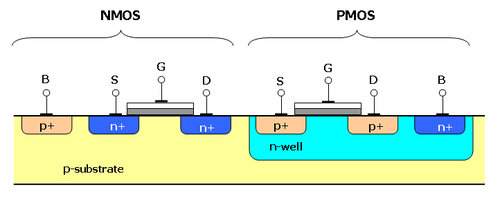

Перед тем как что-то разработать нам нужно понять основу интегральных съем - тразисторы MOSFET. Существую два типа которые мы будем использовать - NMOS и PMOS.

Давайте разберемся как работает тразистор и как он выглядет. Знакомтесь тразистор

Как мы здесь видим у тразистора есть несколько компонентов. Металл и контакт, а также N+ и P Substrate. Когда напряжение Vgs < Vth тогда NMOS закрыт. Когда Vgs >= Vth, а Vds < Vgs - Vth тогда тразистор находиться в линейном режиме. Когда Vgs >= Vth и Vds > Vgs - Vth тогда тразистор находиться в открытом состоянии. Похожим образом работает PMOS но в отличии от NMOS он закрываеться, а не открываеться.

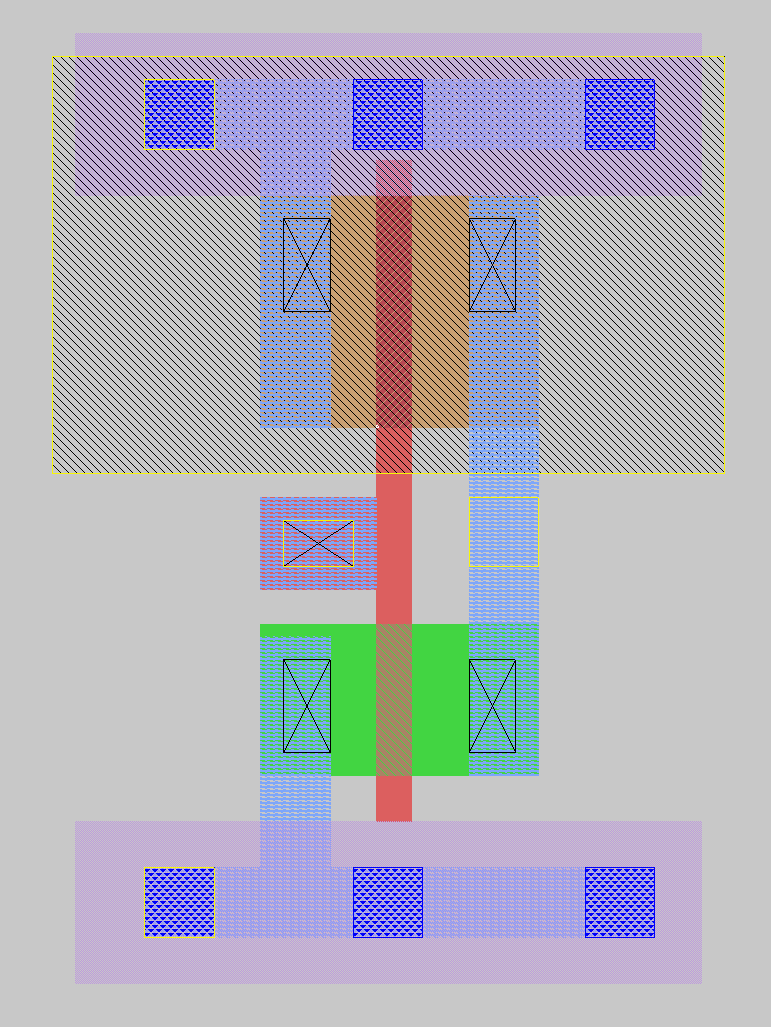

А теперь знакомтесь транзситор PMOS (сверху) и NMOS (снизу)

Разработка аналоговых компонентов

Давайте не буду вас томить. Установите в виртуалкуUbuntu и следуйте следующим шагам։ https://github.com/efabless/openlane#quick-start. Я бы установил его в ~/openlane_exp/ ибо именно этот путь я использую в примере

Для того что бы установить программы которыми мы будем пользоваться следуйте следующим шагам։ https://github.com/armleo/sky130_ubuntu_setup/blob/main/install_tools.sh

Так же вам может быть интересен https://inst.eecs.berkeley.edu/~cs250/fa20/labs/lab1/

Нам нужны следующие программы

OpenLANE, который установит модели для симуляции и отдельные компоненты и примитывы в соответсвующей папке. Почитайте документацию очень интересно. Бесплатная установщик skywater PDK + скрипты для использования разных программ для того что бы в автоматическом режиме скомпилировать вашу цифровую схему. Кроме того образ докера с предустановленными ПО для компиляции.

Yosys. Гордость проектов с открытым исходным кодом. Автор։ Claire Wolf (http://www.clifford.at/). Позволяет скомпилировать ваш Verilog в gate-level представление, которое описывает вашу цифровую схему в виде отдельных компонентов. Замена Design Compiler от Synopsys

Куча других ПО, которые в автоматическом режиме превращают ваш gate-level в GDS-II. Об этом будет в соответсвующей главе

skywater-pdk. Открытый PDK skywater 130nm. Содержит так же так называемые готовые цифровые компоненты, примитивные компоненты и библиотека ячеек ввода-вывода

ngspice, Открытый симулятор spice. На удивление неплохой, но я конечно же рекомендую комерческие симуляторы например HSPICE от Synopsys.

xschem, открытая программа для рисования схем. Бесплатная замена CustomCompiler от Synopsys

klayout, для рисования и открытия GDS-II. Бесплатная замена CustomCompiler от Synopsys

Magic, программа которая может производить DRC, и не только. Вообще очень полезная штука. Бесплатная замена IC Validator от Synopsys

Netgen, программа которая может делать LVS проверку. Бесплатная замена IC Validator от Synopsys

OpenRAM. Компилятор элементов памяти. Замена Memory Compiler от Synopsys. К сожелению мы не можем им пользоваться ибо у нас нет файлов технологической настройки, который закрыты из-за NDA. Правда готовые блоки с синхронными входами и выходами можно найти в https://github.com/efabless/sky130_sram_macros

Давайте уже к практике. Учтите что вам придеться менять много параметров, надеюсь разберетесь.

cd ~/openlane_exp/openlane

docker run -it --rm -v /home/armleo/openlane_exp/openlane:/openLANE_flow \

-v /home/armleo/openlane_exp/openlane/pdks:/home/armleo/openlane_exp/openlane/pdks \

-e PDK_ROOT=/home/armleo/openlane_exp/openlane/pdks \

-e PDKPATH=/home/armleo/openlane_exp/openlane/pdks/sky130A/libs.tech/magic \

-v /tmp/.X11-unix:/tmp/.X11-unix \

-v /home/armleo/openlane_exp:/home/armleo/openlane_exp \

-e DISPLAY=unix$DISPLAY \

-u 1000:1001 efabless/openlane:v0.12

klayout /home/armleo/openlane_exp/openlane/pdks/skywater-pdk/libraries/sky130_fd_sc_hd/latest/cells/inv/sky130_fd_sc_hd__inv_1.gdКоманды сверху установят пример инвертера и запустит докер с проброской из моей домашней папки и проброской X11 для окон.

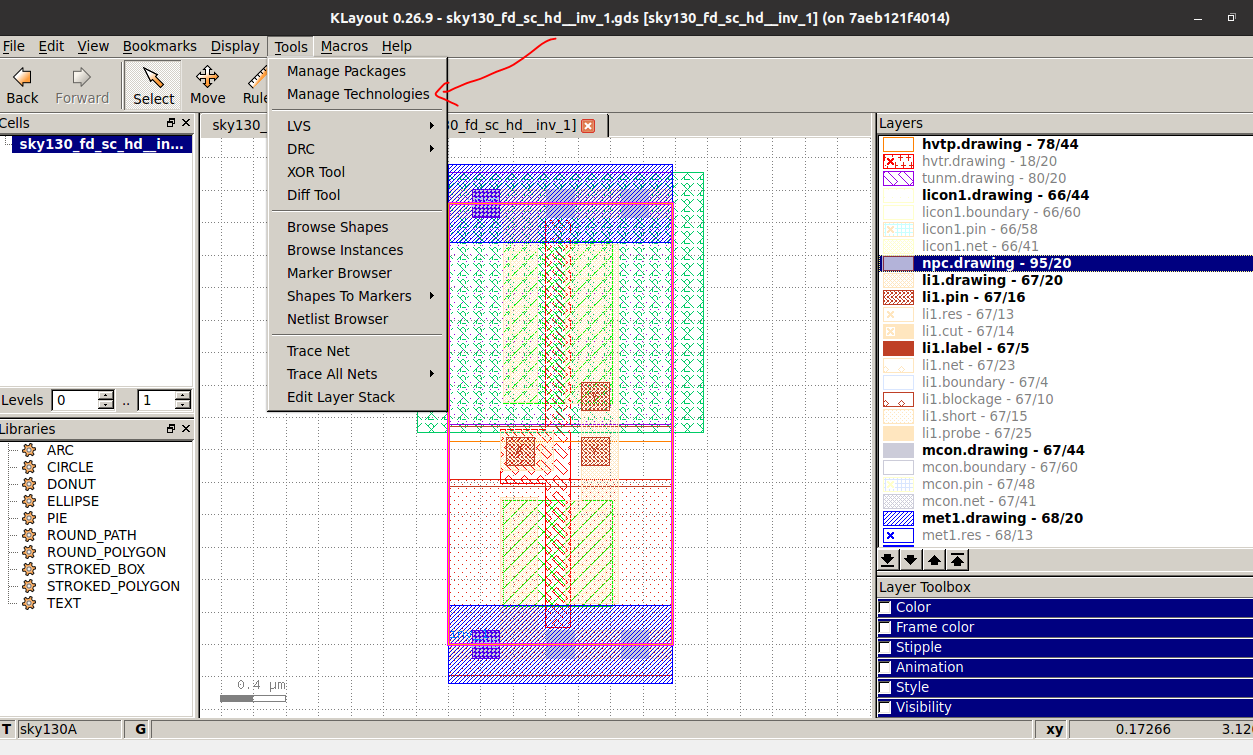

После открытия надо подключить технологические файлы.

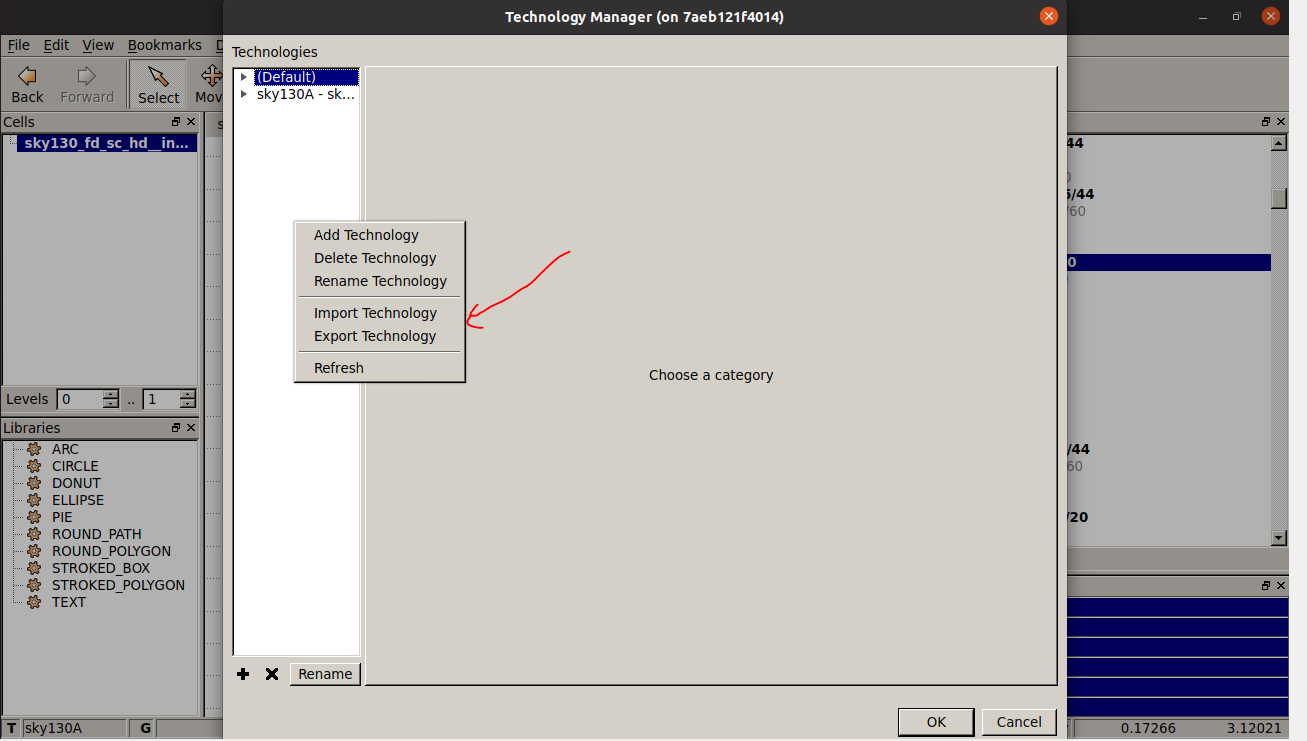

Откройте Manage Technologies

Правый клик по списку технологий

Найдите файл /home/armleo/openlane_exp/openlane/pdks/sky130A/libs.tech/klayout/sky130A.lyt

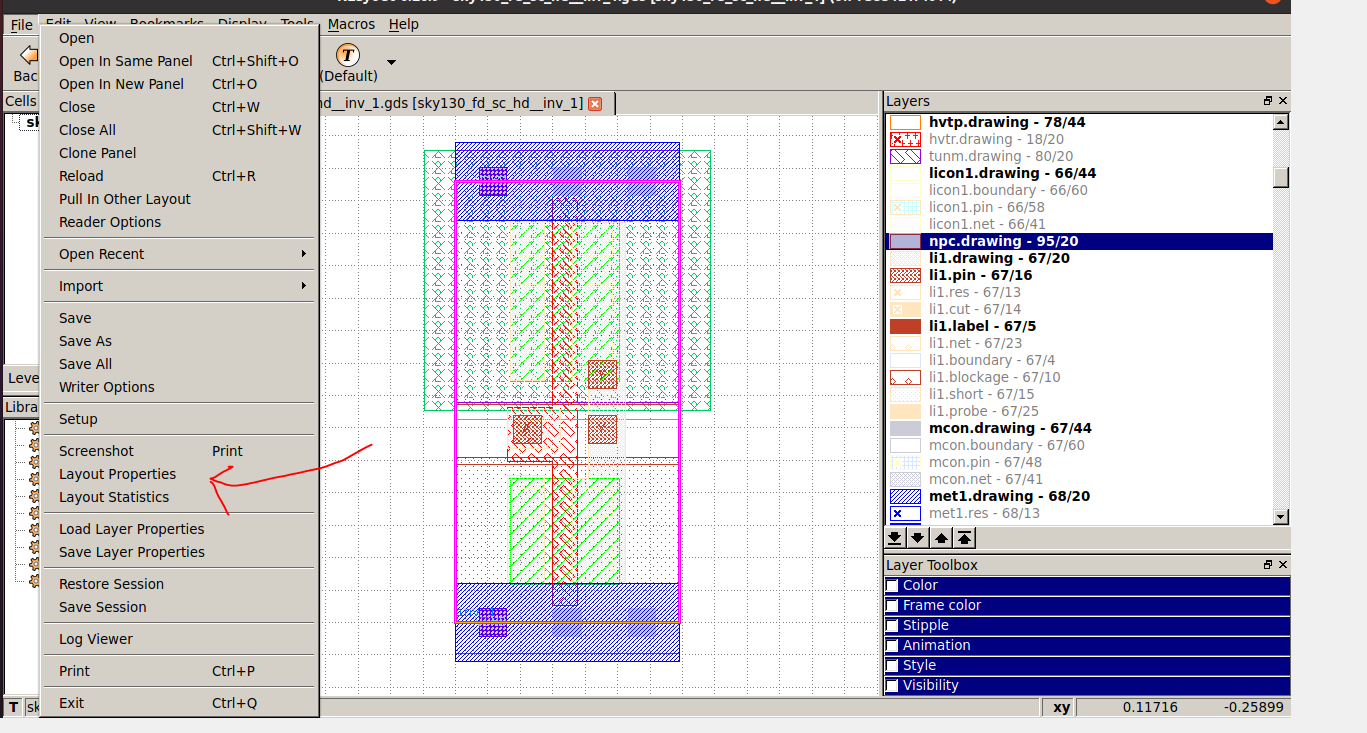

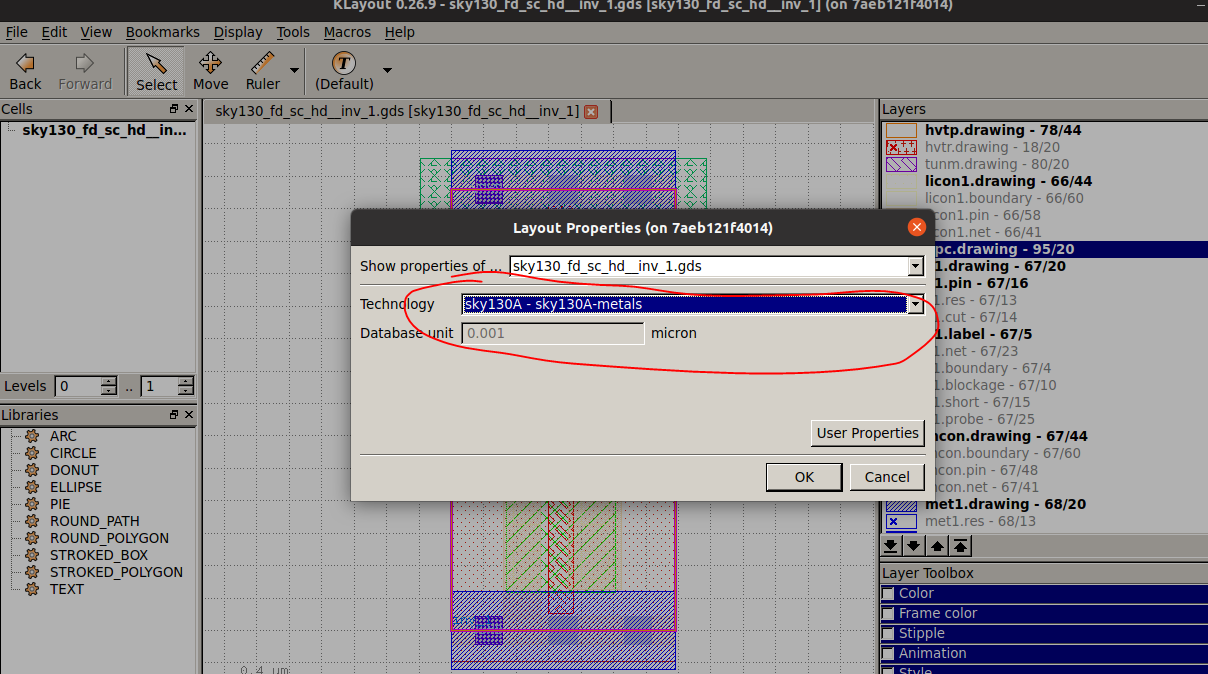

Откройте настройки слоев

Выберите sky130A

Хотите увидеть инвертер?

Да выглядет уродливо, зато бесплатно ։D.

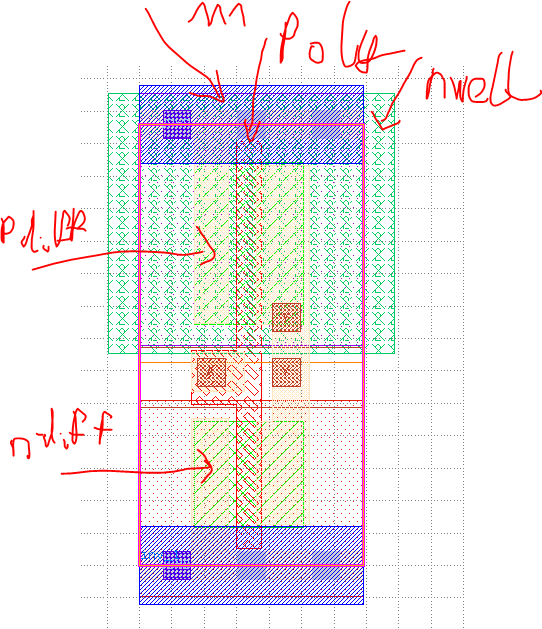

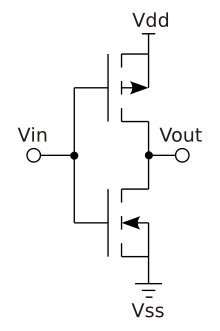

Давайте поймём что это за схема, как она работает и из чего состоит. Сверху синий слой это метал по которому подключаеться SOURCE и BULK ножки PMOS тразистора к VDD или позитивному напряжению. Снизу слой металла по которому идёт VGND или заземление, который подключаеться к ножке SOURCE и BULK NMOS тразистора.

Ножки GATE подключенные к друг другу и к вводному сигналлу A с использованием слойа полисилкона LI1.

Выход подключен к контакту Y с использованием слойа полисилкона LI1.

Инвертер работает следующим образом։

NMOS открыт, когда на входе высокое напряжение, а PMOS закрыт. Таким образом на выходе получаеться низкое напряжение. NMOS открыт, поэтому низкое напряжение подаёться на выход, но короткого замыкания не просиходит, посколько PMOS закрыт.

NMOS закрыт, когда на входе низкое напряжение, а PMOS открыт и VDD подключен к сигналу Y. NMOS закрыт, поэтому низкое напряжение на подаёться не выход, и короткого замыкания не происходит. Таким образом на выходе получаеться высокое напряжение.

Схема в разрезе։

Схема соответсвующая инвертеру։

Здесь вы можете видеть, что у тразистора на самом деле 4 ноги։ DRAIN, SOURCE, GATE, BULK.

В следующей частях разберемся։

как нарисовать несколько компонентов (NAND, NOR), сделать LVS, DRC, PEX и провести симуляцию.

Поймем, что такое последовательные компоненты (Sequential components) - Latch, Flip-flop

После мы разберём как скомпилировать наш Verilog в GDS.

Поймём как собрать нашу схему в Caravel