Прежде чем перейти к статье, хочу вам представить, экономическую онлайн игру Brave Knights, в которой вы можете играть и зарабатывать. Регистируйтесь, играйте и зарабатывайте!

30 октября прошло первое занятие Сколковской Школы Синтеза Цифровых Схем. Из-за Ковида его пришлось провести в онлайн-формате. Трансляция первого занятия:

Возможно онлайн-формат - это и к лучшему, так как в офлайне в Технопарке Сколково есть только 25 посадочных мест, и мы приготовили только 25 FPGA плат, а количество заявок привысило 300. Теперь мы на спонсорские деньги от компании Ядро Микропроцессоры и Максима Маслова @Armmaster заказали еще 100 плат и собираемся их раздать бесплатно для занятий дома, преподавателям вузов и руководителям кружков в других городах.

Чтобы быть уверенным, что получатели плат смогут их использовать, мы поставили в качестве пререквизита их получения прохождение короткого онлайн-курса от Роснано (см. детали в хабрапосте Готовимся к Сколковской Школе Синтеза Цифровых Схем: литература, FPGA платы и сенсоры). 40 с чем-то участников школы прошли этот курс и им будут высланы платы, как только заказанные платы прибудут из Китая.

При этом, так как школа уже началась, а до следующего занятия 13 ноября еще есть время, мы решили попробовать другой пререквизит - решение последовательности коротких задач на верилоге, используя не плату, а бесплатный симулятор Icarus Verilog. Всем участникам, которые собираются дойти в курсе до проектирования процессоров, все равно нужно будет освоить механику кодирования на верилоге, а для этого симулятор просто быстрее, чем учить это на FPGA платах.

Учить верилог в симуляторе Icarus так же просто, как учить программирование на питоне, за исключением того, что у верилога есть синтезируемое подмножество. То есть не все что вы можете сделать в симуляторе вы можете превратить в схему на фабрике или в прошивку в ПЛИС. Кроме этого в верилоге, в отличие от питона, есть физический тайминг, задержки в пикосекундах и максимальная тактовая частота, которые выясняются во время синтеза, то бишь одной симуляцией для обучения не обойтись. Тем не менее, упражнения на симуляторе - это оптимальный способ набить руку на многих вещах.

Идея та же, что научиться игре в шахматы или игре Го с помощью решения большого количества задач в несколько ходов. В качестве справочника для решения верилоговских задач можно использовать учебник Харрис & Харрис (планшетная версия, краткие слайды для лекций), лабник Цифровой Синтез и книгу Дональда Томаса (PDF начала к ней).

Пререквизит для получения плат будет состоять из двух групп упражнений. Первую группу мы уже выложили. Вы можете скачать пакет по ссылке https://bit.ly/chipexpo2021dds22

Упражнения находятся в директории ce2020labs/quizes/problems_001_011. Это 11 файлов на верилоге. В каждом из них вначале пример модуля, потом незаконченный модуль, который вам нужно изменить (с комментарием TODO), а потом тест (модуль testbench). Как работает тест, вам понимать необязательно, про тесты объяснит Александр Силантьев из МИЭТ и Илья Кудрявцев из Самарского Университета на следующем занятии. Пока все что вам нужно сделать - это:

Установить Icarus Verilog по инструкциям ниже. Для него есть версии для Линукса, Windows и MacOS.

Прочитать модуль в начале файла.

Проконсультироваться со слайдами Александра Силантьева с первого занятия, а также возможно с книгами Харрис & Харрис, лабником Цифровой Синтез и книжкой Дональда Томаса, что все это значит.

Прочитать задание под комментарием TODO. Задание я написал на английском, если вы учили в школе другой язык, спросите на телеграм-канале https://t.me/DigitalDesignSchool объяснение задания.

Написать код из нескольких строчек под заданием.

Под Линуксом или MacOS: запустить скрипт run_all_using_iverilog_under_linux_or_macos_brew.sh . Его можно запустить из командной строки в терминале (на Apple тоже есть приложение Terminal если вы не знали) или просто кликнуть на него из менеджера файлов.

Под Windows: запустить пакетный файл run_all_using_iverilog_under_windows.bat . Его можно запустить из командной строки в терминале (на Apple тоже есть приложение Terminal если вы не знали) или просто кликнуть на него из менеджера файлов.

Скрипт или пакетный файл создаст файл log.txt с результатами компиляции и симуляции всех 11 файлов. Если что-то не скомпилировалось, там будет сообщение об ошибке syntax error. Если тест не прошел, там будет сообщение FAIL и информация об ожидаемом значении.

Когда все тесты пройдут, зазипуйте все что вы написали в один файл и пришлите в емейле мне ( yuri@panchul.com с копией yuri.panchul@gmail.com ), Александру Силантьеву в МИЭТ ( olmer.aod@gmail.com ) и Илье Кудрявцеву в Самарский Университет ( rtf@ssau.ru ).

Если что-то непонятно, задавайте вопросы в телеграм-канал.

Задачи можно решать с любым симулятором верилога, который поддерживает SystemVerilog. А также c бесплатным симулятором Icarus Verilog, который хотя и не поддерживает весь SystemVerilog, но поддерживает Verilog 2005 с некоторыми элементами SystemVerilog, достаточных для решения наших задач.

.

Icarus Verilog чаcто используют с GTKWave, программой для работы с временными диаграммами. Для первых десяти задач GTKWave нам не понадобится, но его стоит установить вместе с Icarus Verilog на будущее.

Под Linux Icarus Verilog и GTKWave ставится "sudo apt-get install verilog gtkwave".

Версия Icarus Verilog и GTKWave для Windows здесь.

Icarus можно поставить даже на Apple Mac, что необычно для EDA tools (EDA - Electronic Design Automation). Это можно сделать в консоли с помощью программы brew: brew install icarus-verilog.

Видео установки Icarus Verilog для Windows

Видео установки Icarus Verilog для MacOS

Теперь про первые 11 задачек. Общая тема - мультиплексор - блок выбора. Если селектор стоит в 0, на выход идет значение из входа d0, иначе - значение из входа d1. Но даже такую незамысловатую функциональность в верилоге можно выразить минимум пятью способами:

Через операцию "?" и непрерывное присваивание (continuous assignment) - s001_mux_question.v

Через оператор "if" и блокирующее присваивание внутри комбинационного always-блока - s002_mux_if.v

Через оператор "case" и блокирующее присваивание внутри комбинационного always-блокаs - 003_mux_case.v

Через индекс двумерного массива типа logic - s004_mux_index.v

И даже просто через логические операции и/или/не, вместе с операцией размножения последовательности битов { n { m } } - что значит "построй последовательность состоящую из n копий последовательности m - s005_mux_gates.v

Можно строить большие мультиплексоры с многими входами из мультиплексоров с небольшим количеством входов. Этому посвящено упражнение s006_mux_2n_using_muxes_n.v, которое также вводит иерархию экземпляров модулей:

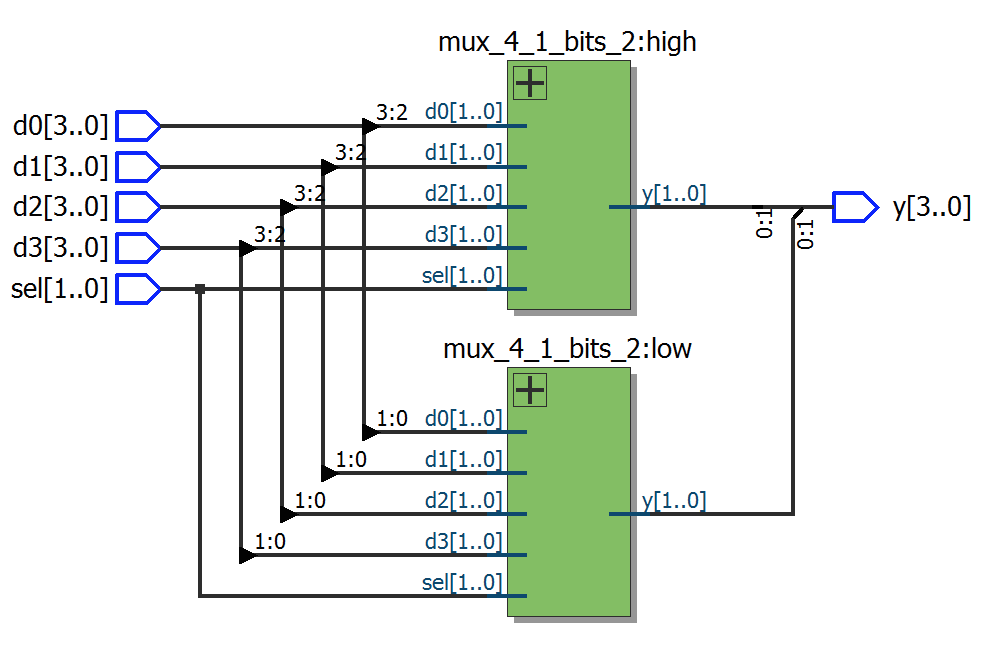

Также можно строить мультиплексоры для широких данных из мультиплексоров для узких данных - про это упражнение s007_mux_using_narrow_data_muxes.v.

Выше мы строили мультиплексоры из логических элементов И, ИЛИ, НЕ. А можно ли строить логические элементы И, ИЛИ, НЕ из мультиплексоров? Это посвящены четыре задачки, в которых нужно построить модули, реализующие комбинационную логику И, ИЛИ, НЕ и ИСКЛЮЧАЮЩЕЕ-ИЛИ (xor) только из мультиплексоров, констант 0 и 1, а также соединений между ними:

s008_not_gate_using_mux.v

s009_and_gate_using_mux.v

s010_or_gate_using_mux.v

s011_xor_gate_using_mux.v

Я не обещаю, что мы дойдем до задачи номер 999 (наверное это будет алгоритм Томасуло, который показывает девушка Ирина на рисунке 7.71 на фотографии ниже, и про который любят спрашивать недавних студентов на собеседованиях в электронные компании) но мы будем работать в этом направлении. Загружаем, приступаем и ждем вас на занятии 13 ноября, которое по-видимому начнется с разбора этих задачек.