Прежде чем перейти к статье, хочу вам представить, экономическую онлайн игру Brave Knights, в которой вы можете играть и зарабатывать. Регистируйтесь, играйте и зарабатывайте!

В техноиндустрии количество транзисторов и плотность транзисторов часто используют для демонстрации технического достижения и некой вехи в развитии. После выхода нового процессора или системы на чипе многие производители начинают хвастать сложностью своей схемы, измеряя количество транзисторов в ней. Недавний пример: когда компания Apple выпустила iPhone 11 с A13 Bionic внутри, она похвалялась тем, что процессор содержит 8,5 млрд транзисторов. В 2006 Intel сходным образом хвасталась Montecito, первым процессором с миллиардом транзисторов.

По большей части это постоянно увеличивающееся количество транзисторов является следствием закона Мура и мотивацией к дальнейшей миниатюризации. Индустрия переходит на новые техпроцессы, и количество транзисторов на единицу площади продолжает расти. Поэтому количество транзисторов часто считается показателем здоровья закона Мура, хотя это на самом деле и не совсем корректно. Закон Мура в оригинальном виде – это наблюдение, согласно которому количество транзисторов экономически оптимального дизайна (т.е. с минимальной стоимостью одного транзистора) удваивается каждые два года. С точки зрения потребителя, закон Мура – это на самом деле обещание того, что завтрашние процессоры будут лучше и ценнее сегодняшних.

В реальности плотность транзисторов значительно колеблется в зависимости от типа чипа, и особенно от способа компоновки самого чипа. Что ещё хуже, не существует стандартного способа подсчёта транзисторов, из-за чего для одной и той же схемы эти цифры могут отличаться на 33-37%%. В итоге количество транзисторов и плотность транзисторов – это лишь приблизительные метрики, и если замкнуться только на них, можно потерять из виду общую картину.

На компоновку продукта влияет его предназначение

Плотность транзисторов тесно связана с предназначением и стилем разработки продукта. Будет, по меньшей мере, некорректно сравнивать такие сильно отличающиеся друг от друга компоновки, как ASIC с фиксированным быстродействием (к примеру, Broadcom Tomahawk 4 25.6Tb/s или Cisco Silicon One 10.8Tb/s) и высокоскоростной процессор для дата-центров (к примеру, Intel Cascade Lake или Google TPU3).

От ASIC требуется поддержка определенной пропускной способности, а увеличение частоты не приносит ему пользы. К примеру, чип Cisco Silicon One предназначен для высокоскоростных сетей, использующих 400Gbps Ethernet, и от увеличения частоты на 10% он ничего не выиграет. 400Gbps – это стандарт IEEE, а следующая ступень скоростей – уже 800Gbps. В итоге большинство команд разработки ASIC оптимизируют чипы по минимуму стоимости, автоматизации инструментов разработки, уменьшению количества специальных схем и плотности транзисторов.

И наоборот, чем быстрее серверный чип, тем больше он стоит, и поэтому он всегда будет получать преимущество от увеличения частоты. К примеру, Xeon 8268 и 8260 – 24-ядерные процессоры, и отличаются в основном базовой частотой (2,9 ГГц и 2,4 ГГц), в результате чего их стоимость отличается на $1600. Поэтому команда разработки серверов будет стремиться к оптимизации по частоте. Высокоскоростные процессоры обычно используют больше специальных схем и более крупные транзисторы. В современных схемах на базе FinFET это даёт увеличение количества транзисторов с 2, 3 плавниками, и даже больше. И наоборот, низкоскоростная логика, типа параллельных GPU или ASIC чаще использует более плотную компоновку транзисторов всего с одним плавником, принося в жертву тактовую частоту для увеличения плотности. Транзисторы с низкой утечкой также обычно имеют больший размер.

Плотность и количество транзисторов определяются балансом разработки

Ещё больше влияет на количество транзисторов и плотность транзисторов реальная компоновка чипа. Каждый современный чип состоит из какой-то комбинации логики для вычислений, памяти (обычно SRAM) для хранения и I/O для передачи данных. Однако по плотности три этих компонента значительно разнятся – см. таблицу 1. У Poulson и Tukwila одна платформа, одинаковые цели, связанные с высокой скоростью работы, и высочайший уровень надёжности.

Таблица 1: количество транзисторов и плотность транзисторов основных участков поколений Poulson и Tukwila процессора Itanium

Процессоры состоят из четырёх основных участков: ядра CPU, кэш L3, системный интерфейс и I/O. Судя по раскрытой производителем информации, у Poulson на кристалле есть ещё 18 мм2 для других функций. Участок ядер CPU содержит ядра и оптимизированные по быстродействию кэши L1 и L2, и основное место там занимает высокоскоростная логика для операций свыше 1,7 ГГц для Tukwila и 2,5 ГГц для Poulson. Крупные кэши L3 (24 Мб для Tukwila и 32 Мб для Poulson) разработаны для максимальной ёмкости и используют самые плотные ячейки 6T SRAM из возможных. В системном регионе находится большой ассортимент функций – матричный переключатель для передачи данных I/O и памяти по кристаллу, QPI и контроллеры памяти, протокол когерентности с использованием справочника и кэши справочника, модули управления питанием. Системный участок обычно не такой плотный, поскольку логика там работает на фиксированной частоте, и во многих из более крупных компонентов высокоскоростные шины, пересекающие кристалл, занимают больше места, чем транзисторы. И, наконец, регион I/O содержит физические интерфейсы для внешних коммуникаций, реализованных через высокоскоростные последовательные связи (QPI links). Связи по-разному передают сигналы, и в сумме у них набирается порядка 600 контактов.

В количественном плане два этих процессора иллюстрируют критически важные тренды, которых придерживаются практически все крупные разработчики чипов. Во-первых, в различных частях чипа плотность транзисторов может отличаться в разы – более, чем в 20 раз, что во много раз больше, чем упоминаемое в законе Мура удвоение плотности, связанное с улучшением процессоров на одно поколение. Естественно, самым плотным участком является регион кэша, состоящий из сверхплотной SRAM – он и содержит большинство транзисторов. Кэш примерно в 3-5 раз плотнее, чем вычислительная логика в ядрах, что опять-таки больше, чем удвоение. Наименее плотная часть – это I/O, поскольку там содержатся деликатные аналоговые схемы типа PLL и DLL, цифровые фильтры, и крупные I/O транзисторы высокого напряжения, которые используются для отправки данных с чипа и получения им данных. Кроме того, многие участки I/O должны занимать достаточно места по краям чипа, чтобы их можно было соединить со всеми контактами, и занимаемая ими площадь определяется количеством контактов, а не плотностью схем.

Данные выше демонстрируют, что плотность транзисторов современных чипов является в основном функцией их предназначения и компоновкой самого чипа. Для экстремального примера представьте себе 32 нм схему, основанную на Poulson, но не имеющую кэша L3 – плотность транзисторов такого чипа равнялась бы примерно 2,57 млн/мм2, или менее половины реальной плотности Poulson. И в другую сторону – гипотетический вариант Poulson, содержащий только вычислительную логику и кэш, без системы I/O, имел бы плотность транзисторов порядка 9 млн/мм2.

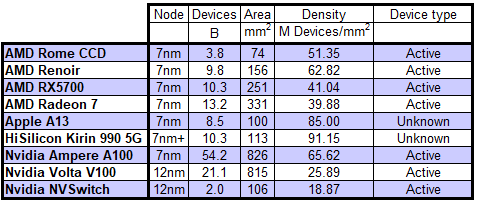

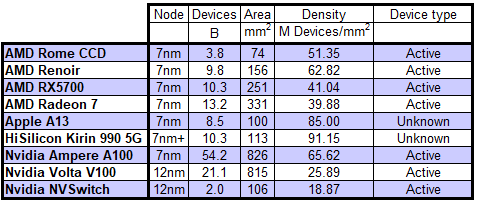

Таблица 2: количество транзисторов и плотность транзисторов для некоторых чипов на 7 нм и 12 нм, по сообщению производителей

В таблице 2 содержатся подробности о нескольких чипах, произведённых по техпроцессам 7 нм и 12 нм от TSMC, подчёркивающие влияние компоновки чипа на плотность транзисторов. Radeon VII и RX 5700 от AMD похожи по компоновке, используют один техпроцесс, и их плотность транзисторов почти одинаковая. Плотность транзисторов у AMD Renoir и Nvidia A100 в 1,5 раза больше – возможно, поскольку это было целью разработчиков, или, возможно, благодаря более современным инструментам разработки. Ещё одно полезное сравнение — Nvidia V100 GPU и NVSwitch, 18-портовый коммутатор от NVLink. Техпроцесс у них один, однако последний в основном ориентирован на I/O, и в результате плотность транзисторов у V100 в 1,37 раза больше, чем у NVSwitch.

Наконец, SoC от двух смартфонов в 1,35 – 2,29 раз плотнее, чем остальные процессоры на 7 нм. Эта впечатляющая плотность достигнута благодаря разным целям оптимизации. SoC смартфонов делают так, чтобы они были подешевле, а их плотность была повыше. Процессоры AMD стремятся к высокой производительности. Кроме того, компании Apple и HiSilicon крупнее и богаче, они могут позволить себе большие команды разработчиков и большие траты на оптимизацию. Однако возможно также, что количество транзисторов и плотность транзисторов у мобильных SoC отличаются потому, что для них транзисторы считают по-другому. Последний столбец таблицы 2 показывает, как именно производитель подсчитывает количество транзисторов – мы подробнее обсудим это чуть позже.

Не все транзисторы созданы равными

Ещё одна проблема использования подсчёта количество транзисторов или плотность транзисторов в качестве метрики состоит в том, что эти цифры неоднозначны и могут ввести в заблуждение. Обычно мы представляем себе транзисторы в виде физической реализации логических блоков и схем. При вычислениях этим можно обозначить всё что угодно – от ядра процессора или модуля работы с плавающей запятой до инвертера. Для хранения это может быть кэш, регистровый файл, ассоциативное запоминающее устройство (content-addressable-memory, CAM) или битовая ячейка SRAM. Для аналоговых компонентов или I/O это может быть PLL, или передатчик/приёмник, расположенные вне чипа. Транзисторы, физические реализующие эти блоки, называют активными транзисторами (в отличие от схематических транзисторов). Однако в реальности не все транзисторы созданы равными, и современные процессоры производятся со множеством неактивных транзисторов. Транзисторы, формирующиеся в процессе изготовления называют макетными. Макетные транзисторы – это описанные выше активные транзисторы, но также среди них есть и фиктивные транзисторы, а также транзисторы, используемые в качестве развязывающих конденсаторов.

Фиктивные транзисторы вставляют в схему для повышения эффективности производственного процесса. К примеру, определённые шаги отжига и травления в процессе производства лучше работают на относительно однородной поверхности, и если вставить дополнительные транзисторы в пустые места, это увеличит однородность. Для многих аналоговых схем такие транзисторы нужны для достижения желаемой эффективности. Ещё пример – эффективность современных FinFET зависит от нагрузки на транзисторы, являющейся функцией транзисторов, находящихся поблизости. Для достижения нужной эффективности иногда приходится разместить несколько транзисторов поблизости, чтобы получить нужную нагрузку.

Хотя фиктивные транзисторы повсеместно применяются, их используют не так уж много. А вот развязывающие конденсаторы на основе MOSFET используются повсеместно. В целом логика современного чипа никогда не достигает 100% пространственной эффективности. При всех чудесах современных средств разработки всё равно останутся пустые места между отдельными логическими ячейками (к примеру, между вентилями NAND), между функциональными модулями (кэш L1D), и даже между целыми блоками (например, ядрами CPU). Пустое пространство возникает вследствие того, что инструменты разработки пытаются удовлетворить правилам, гарантирующим эффективное производство и частоту, использовать доступные ресурсы (например, маршрутные слои) и собрать электромеханическую головоломку из логических клеток, функциональных модулей и блоков. Пустое пространство может занять до 10-25% чипа. Для увеличения выхода годных изделий кристаллы должны быть относительно однородными, и пустое пространство не может оставаться реально пустым. Многие схемы заполняют эти места развязывающими конденсаторами, чтобы улучшить обеспечение питанием. Кроме того, в некоторых схемах развязывающие конденсаторы располагают внутри стандартных библиотек ячеек. Транзисторы в роли развязывающих конденсаторов – основной источник неактивных макетных транзисторов, однако точные данные по их количеству сложно найти.

Наши друзья из TechInsights провели технический анализ процессора на уровне схемы, в который входил и подсчёт макетных транзисторов на небольшом участке кристалла. Они поделились своими открытиями для небольшого списка SoC на 7 нм. Данные основаны на небольшом количестве избранных мест с каждого из SoC, обычно с GPU, где плотность транзисторов должна быть наибольшей. Они обнаружили, что в изученных ими местах порядка 70-80%% транзисторов были активными, а оставшиеся 20-30%% — развязывающими конденсаторами или фиктивными. Однако эти цифры основаны на небольшом количестве выборок, поскольку подобный анализ требует большого количества денег и времени. Чтобы подтвердить эти цифры и развить тему, мы собрали данные по нескольким современным схемам, и обнаружили, что обычно процент активных транзисторов составляет 63-66 от общего количества, а 33-37%% транзисторов – развязывающие конденсаторы. Числа у TechInsights получились ниже, вероятно, потому, что они изучали наиболее плотные логические участки SoC, и не учитывали пустое пространство, где могло оказаться больше развязывающих конденсаторов.

Таблица 2: количество транзисторов и плотность транзисторов для некоторых чипов на 7 нм и 12 нм, по сообщению производителей

Из этих данных совершенно ясно следует, что между количеством активных и макетных транзисторов в чипе часто есть большая разница. К сожалению, многие компании обычно не указывают, число каких транзисторов они учитывают. Данные по процессорам от AMD и Nvidia из Таблицы 2 взяты из технических документаций. На основе неформального обсуждения этого вопроса с двумя этими производителями, мы привели число активных транзисторов в последнем столбце. Судя по всему, число транзисторов, указанное для HiSilicon Kirin 990 5G, может означать макетные транзисторы, что может объяснить несоответствие между этими схемами. Непонятно, реализован ли чип Apple A13 с использованием 8,5 млд активных или макетных транзисторов. В первом случае их достижение по плотности было бы впечатляющим.

Кажется неразумным учитывать эти фиктивные транзисторы и развязывающие конденсаторы наравне с активными транзисторами. Активные транзисторы реализуют функции и особенности, ценимые пользователями – будь то ядра CPU, выборочное отключение питания для улучшения энергопотребления в режиме простоя, ускорители нейросетей или кэш. Однако фиктивные транзисторы и развязывающие конденсаторы – это просто лишние компоненты, не добавляющие прямой ценности, а в некоторых случаях даже проигрывающие более сложным технологиям. К примеру, траншейные конденсаторы от IBM гораздо эффективнее развязывающих конденсаторов, и позволяют создавать плотные чипы eDRAM, уменьшая стоимость системы. Intel FIVR увеличивает эффективность платформы и полагается на MIM-конденсаторы, практически устраняя необходимость в развязывающих конденсаторах, а также, вероятно, уменьшает количество развязывающих конденсаторов, необходимых на кристалле. В обоих случаях уменьшение количества развязывающих конденсаторов приносит пользу. Суть закона Мура состоит в том, чтобы создавать ценность для потребителей, продуктивно используя дополнительные активные транзисторы, а фиктивные транзисторы и развязывающие конденсаторы этой ценности не добавляют.

Дело не в том, сколько там транзисторов, а в том, как вы их используете

Подводя итоги, Становится видно, что количество транзисторов и плотность транзисторов – метрики весьма проблемные. На них сильно влияет общая компоновка чипа и объёмы критически важных блоков – вычислительной логики, SRAM, I/O. SRAM наиболее плотная из всех трёх, поэтому небольшое изменение размера кэша сильно изменит количество транзисторов, при этом практически не повлияв на быстродействие и ценность. Более того, не все макетные транзисторы созданы равными. Активные транзисторы – это фундаментальные строительные блоки таких ценных компонентов, как CPU и GPU. С другой стороны, фиктивные транзисторы и развязывающие конденсаторы больше похожи на лишний груз. Надеюсь, что большинство компаний не будут объединять активные и макетные транзисторы, но важно отличать два этих типа при сравнении схем.

Несмотря на все проблемы с количеством транзисторов, эта метрика потенциально полезна в очень редких случаях. Почти всегда процессор с 100 млрд транзисторов будет сложнее и ценнее процессора с 100 млн транзисторов. Вероятно, анализ всё ещё остаётся верным для двукратной разницы в количестве транзисторов – особенно для чипов, обрабатывающих задачи параллельно, типа GPU, или для двух очень похожих процессоров (к примеру, двух SoC для смартфонов или двух серверных процессоров). Но сложно поверить, что небольшое различие в количестве транзисторов обязательно приведёт к наличию разницы в ценности. На самом деле отличным примером могут служить Radeon VII и RX 5700 от AMD. У Radeon VII на 28% больше транзисторов, однако быстродействие у него почти такое же, в частности из-за того, что в линейке RX 5700 используется более современная архитектура. Кроме того, RX 5700 оказывается гораздо дешевле, поскольку использует GDDR6 вместо HBM2. Реальная ценность для потребителей заключается не в количестве транзисторов, а в том, как они используются. Небольшие различия в количестве транзисторов не имеют значения по сравнению с хорошей архитектурой, выбором функций и другими факторами.

Многие из этих критических утверждений верны и для плотности транзисторов, и для техпроцессов. Если небольшое увеличение в количестве транзисторов не обязательно влияет на пользовательскую ценность, то вряд ли на это повлияет соответствующее небольшое увеличение в плотности. С другой стороны, такие факторы, как эффективность транзисторов, динамическое питание, энергопотребление в простое, инструменты разработки, доступность подложек и передовые свойства могут придать большую ценность. Плотность – всего лишь один из множества аспектов процесса, и если зацикливаться на нём, то можно за деревьями не заметить леса.