Я решил написать эту заметку на Хабре по-русски и по-английски, чтобы раздавать ссылку на нее как в англо- так и в русско-язычные форумы и группы. Русский текст не является переводом английского и наоборот — я просто написал заметку дважды (терпеть не могу переводить). Желающие покритиковать мой английский сразу направляются в конец поста, где они будут шокированы моим акцентом в длинном многочасовом видео. Я рассматриваю свой акцент не как bug, а как feature. Мы все знаем, что многие американки считают например носоглоточный британский акцент привлекательным. Настала пора придать такой же статус и суровому русскому акценту. Для этого нужно как можно большему количеству русских произносить речи на разнообразных международных мероприятиях. Наш пароль «лет ми спик фром май харт».

Но сначала о выставке.

Миллионы потребителей гаджетов всей планеты следят за выставкой Consumer Electronics Show (CES), которая проходит в Лас-Вегасе в январе. Они, никогда не знавшие, что такое D-триггер, важно рассуждают, чем четыре гигагерца лучше чем три в последних процессорах от AMD и Qualcomm-а. Но есть выставка, ориентированная не на потребителей, а на разработчиков электроники. Эта выставка называется Design Automation Conference (DAC), и она в некоторые годы тоже проходит в Лас-Вегасе, но не в декабре, а в июне.

Millions of gadget lovers every year watch the Consumer Electronics Show (CES) which takes place in Las Vegas in January. Those folks, who never learned the function of a D-flip-flop and how the static timing is calculated, discuss gigahertz frequencies after reading the latest articles in Wired magazine they perceive as a technical publication. However there is another conference, not for the consumers, but for the creators of electronics. This conference is called the Design Automation Conference (DAC) and it also takes place in Las Vegas, although not every year, and not in January, but in June.

The industry of Electronic Design Automation (EDA) makes software for hardware designers. EDA is controlled by three large companies: Synopsys, Cadence and Mentor Graphics (now a part of Siemens). Both Synopsys and Cadence have a complete set of products, necessary to design and simulate a digital chip on multiple levels. The design flow, called RTL2GDSII, starts from specification and coding the circuit's cycle behavior in hardware description language (Verilog or VHDL), proceeds with synthesizing this description into a graph of logic elements (netlist), then continues to placing the netlist into a physical blueprint of the chip and routing on-chip wires to connect the standard cells, the building blocks of ASICs (Application-Specific Integrated Circuits).

Индустрию автоматизации проектирования электроники доминирует три крупные компании: Synopsys, Cadence и Mentor Graphics (которую пару лет назад купил Siemens). Synopsys и Cadence создали софтвер, который покрывает весь маршрут проектирования RTL2GDSII. Этот маршрут я кратко описал в моей предыдущей заметке про DAC четыре года назад:

В последние2530 лет дизайн микросхемы чаще всего пишется на языке описания аппаратуры Verilog (в Европе и у военных — VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. — получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

John Sanguinetti, a Verilog guru since 1980s. John was a founder of a company called Chronologic Simulation which, back in 1990s, created VCS, a Verilog Compiled code Simulator. This simulator is now a property of Synopsys. VCS is used by a majority of large electronic companies. VCS brought to Synopsys billion dollars in revenue.

Вот в стороне от выставочного зала сидит Джон Сангвинетти — ранний гуру верилога со времен 1980-х и основатель компании Chronologic Simulation. Эта компания подарила миру быстрый симулятор верилога VCS (Verilog Compiled code Simulator), который сейчас является собственностью компании Synopsys. Этот симулятор используют большинство крупных разработчиков чипов. VCS принес Synopsys-у миллиарды долларов:

Mentor Graphics is now a part of Siemens, the third-largest EDA company. Unlike Synopsys and Cadence, Mentor Graphics does not have a full line of RTL2GDSII tools. Its two most recognized streams of revenue come from Calibre, a set of physical design verification tools, and Veloce, a hardware emulator. Calibre includes for example a tool that checks geometric design rules (width, spacing, enclosure) on the final «blueprints» of the chip. Veloce uses FPGA-like chips that

Mentor Graphics, третья по величине компания индустрии EDA, в конце 2016 года стала частью Siemens-а. В отличие от Синопсиса and Кейденса, у Ментора нет всей цепочки программ, которые покрывают маршрут RTL2GDSII. Два крупных источника дохода Mentor-а — это комплекс программ Calibre, который делает проверки на финальной стадии проектирования микросхем, и эмулятор Veloce (произносится «Велочи»). Пример проверки в Calibre — минимальное расстояние между дорожками на микросхеме

UPD: поправил на основе коммента amartology: Антенна — это вообще про другое. Она возникает, когда одна дорожка становится такой большой, что начинает работать как антенна, принимая во время производства сигнал на частоте колебаний плазмы для травления.

А эмулятор Veloce использует ПЛИС-образные ASIC-и для быстрой

In addition to highly profitable Calibre and Veloce projects, Mentor always had a large number of other projects, products, services, trainings and educational programs. For example Mentor is cultivating the field of functional verification, a critically important part of the digital design workflow.

Помимо сильно прибыльных проектов типа Calibre и Veloce, в Менторе есть масса других проектов, продуктов, сервисов, исследовательских проектов и образовательных программ. Например, в Менторе занимаются функциональной верификацией — критически важной частью производственного процесса:

A number of small companies, including Doulos, Willamette HDL and Sunburst Design, sell hardware verification training to large and medium-size electronic companies. Such niche exists because universities do not teach the art of functional verification properly and do not adopt new technologies, such as SystemVerilog, UVM, formal verification using concurrent assertions, Portable Stimulus, etc in their curriculum for decades. Even Stanford does not have it in their curriculum as far as I know from talking with their graduates.

На функциональной верификации кормятся несколько небольших компаний, которые продают трейнинги по SystemVerilog и UVM большим корпорациям по освежающе высоким ценам, типа пара тысяч долларов на человека. У ним относятся Doulos, Willamette HDL, Sunburst Design и другие:

Another small company called Verific. They have just a handful of people but they are very successful in their niche. Verific sells SystemVerilog parsers adopted by important EDA companies, both large and small.

Вот еще одна небольшая, всего несколько человек, но очень успешная в своем роде компания, которая называется Verific. Она продает парсер Verilog-а, который используют многие EDA компании:

The founder of Verific gives an interview to a popular EDA website called EDA Cafe. There are several other popular EDA websites including John Cooley's deepchip.com but I did not meet John Cooley on DAC floor this time.

Вот основатель Verific дает интервью популярному в это индустрии вебсайту EDA Cafe:

Now let's talk about FPGA.

Теперь поговорим про ПЛИС, они же ППВМ (сейчас меня будут поправлять), они же FPGA.

Что это такое, я также кратко описал в моей предыдущей заметке про DAC четыре года назад:

В самом простом варианте FPGA состоит из матрицы однородных ячеек, в функцию каждой из которых можно поменять с помощью мультиплексоров, подсоединенных к битам конфигурационной памяти. Одна ячейка может стать гейтом AND с четырьмя вводами и одним выводом, другая — однобитным регистром и т.д. Загружаем в конфигурационную память последовательность битов из памяти — и в FPGA образуется заданная электронная схема, которая может быть процессором, контроллером дисплея и т.д.Two largest producers of FPGA are Xilinx and Altera, now a part of Intel.

ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер).

Две крупнейшие компании, которые выпускают FPGA — это Xilinx и Altera, сейчас часть Интела:

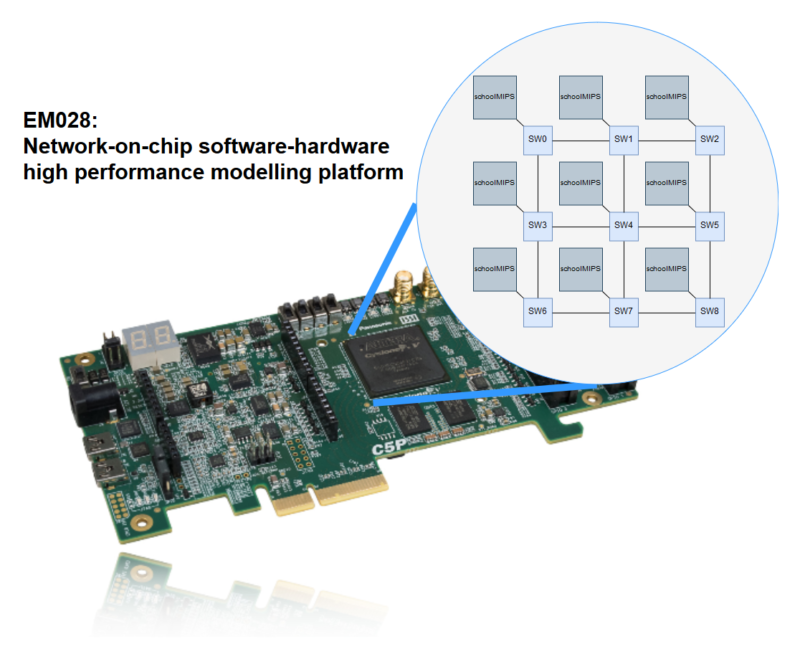

These week Intel collects votes for the first round of Innovate FPGA contest. One of Russian entries uses a mesh of tiny schoolMIPS processor cores. schoolMIPS implements a subset of MIPS architecture. It exists in several variants, including single-cycle with no data memory (the simplest one), a version with interrupts, a pipelined version, etc:

Кстати, на этой неделе Интел проводит голосование на конкурсе Innovate FPGA, в котором участвуют в том числе и российские команды. Один из проектов — NoC-based multiprocessing system prototype. Это прототип сети на кристалле с большим количеством узлов на основе процессоров Станислава Жельнио sparf (по книге Харрис & Харрис «Цифровой синтез и архитектура компьютера») https://github.com/MIPSfpga/schoolMIPS. Делает студент 4 курса МИЭМ НИУ ВШЭ:

The world of FPGAs is not limited to Xilinx and Altera / Intel. There are several much smaller vendors, like Lattice and Microsemi / Actel, and even small companies that do not design the end chips themselves bit license the design of FPGA cell blocks to ASIC companies. A useful application would be to create a reconfigurable coprocessor connected to a fixed high-frequency CPU core. Another application is security: some companies wants to hide their secrets in reconfigurable logic rather then to show the layout of their fixed logic to a motivated researcher with electron microscope and a lot of time.

Но в мире FPGA есть игроки и поменьше, например вот две компании, которые лицензируют дизайн блоков FPGA, которые можно встраивать в многотиражные фиксированные микросхемы для придания им гибкости.

Every DAC has several FPGA board vendors. Not the vendors of cheap student boards like Digilent and Terasic, that start from $55, but FPGA boards for ASIC prototyping that can cost $30,000, $100,000 or more.

На DAC традиционно присутствуют производители плат FPGA. Они продают не дешевые студенческие платы за $55 долларов, а серьезные FPGA платы за $55 _тысяч_ долларов и выше. Их клиент — не студент, а суровый коллектив разработчиков ASIC-а, который использует большие платы для прототипирования.

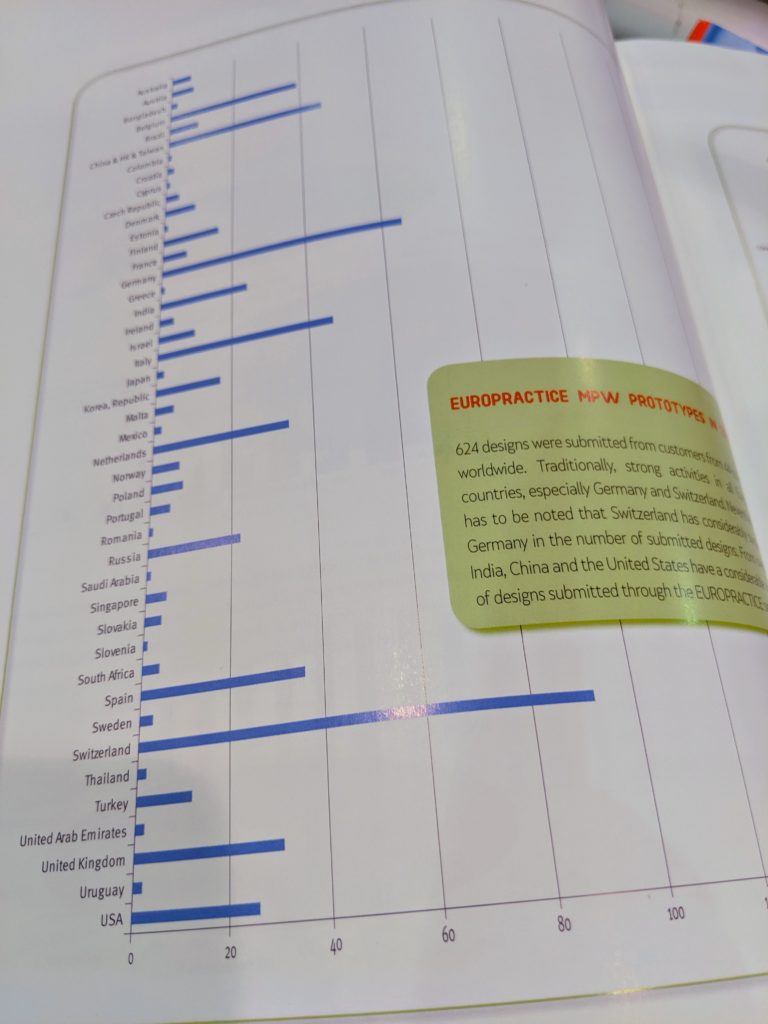

What if a researcher did some proof of concept using FPGA and now wants to manufacture his own ASIC? A typical commercial order to manufacture an ASIC usually requires the initial payment from ~$300K to ~$3,000,000 depending on process technology. However there are specialized companies, Europractice in Europe and MOSIS in US, that sell small quantity «shuttle» services, or multi-project wafer (MPW) services, starting with just $3000 for 180nm technology or just tens thousand dollars for something modern, like 28nm.

А что если студенту или суровой компании захотелась сделать настоящий ASIC на фабрике, а денег мало или жалко? Или, если не жалко, то это тестовый чип или совсем небольшая партия? Для этого в Америке есть компания MOSIS, а в Европе — Europractice. Несколько тысяч долларов — и у вас в руках спроектированный вами чип на технологии типа 180 нанометров. Пару десятков тысяч — и у вас в руках ваш чип на более свежей технологии, например 28 нанометров, как у пятого Айфона. Замечу что за массовое коммерческое производство начальный платеж фабрике от сотен тысяч долларов для старых технологий до двух-трех миллионов для новых.

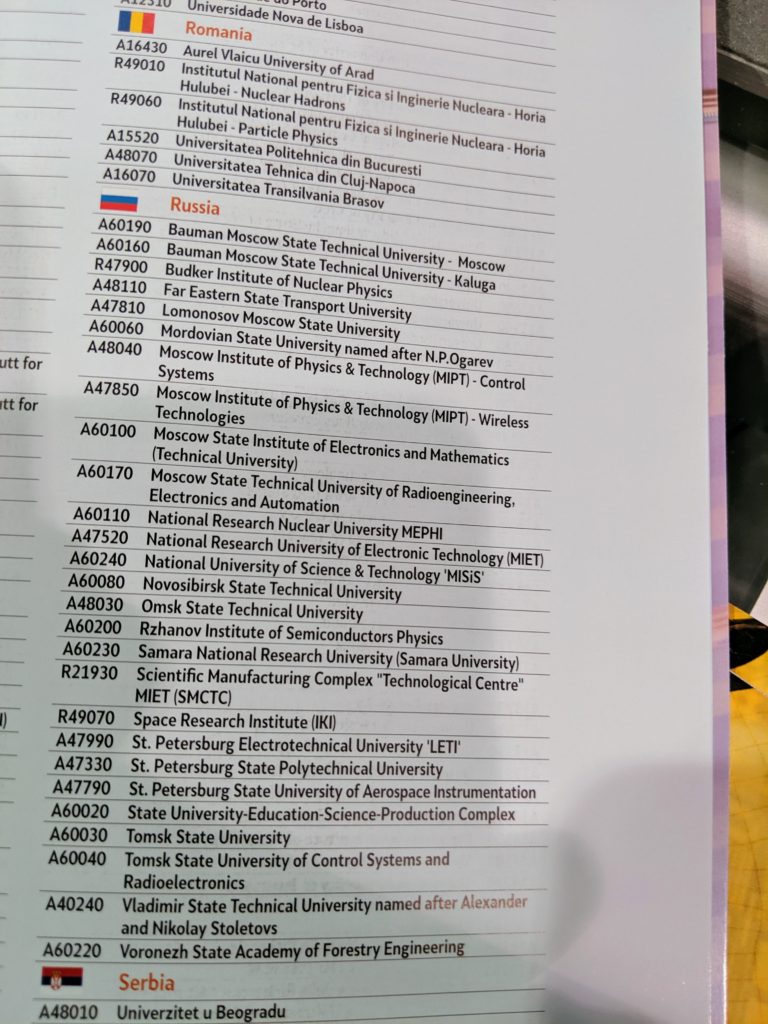

Интересно что у Europractice есть клиенты в России, даже в Омске. Признавайтесь, кто в Омске проектирует ASIC-и.

Europractice has a number of Russian companies, including somebody in Omsk:

There are companies with business models that are somewhat mysterious to me. For example I don't understand how this company below can survive on a niche Eclipse plugin. I guess they get most revenue selling some consulting services.

Существуют компании, про которые я не понимаю, как они зарабатывают. Например вот эта продает очень нишевый плагин к Eclipse. Наверняка они живут не на него, а на какой-нибудь консалтинг.

Another niche company with non-obvious business model. They translate a description of software-visible registers into Verilog glue logic and other interface files. I guess this company may have some Cisco-type large customer that got hooked on their technology long time ago and pay them since then.

Еще одна нишевая компания с неочевидной бизнес моделью. Транслируют описание доступных программисту регистров в верилог и интерфейсные файлы. Наверное, у них есть какой-нибудь крупный клиент типа Cisco, который когда-то много лет назад запал на их тул, и с тех пор платит, так как менеджменту клиента облом нанимать своего инженера.

A melancholic gentleman from Huawei described their achievements in networking chips. Huawei is obviously dependent on US EDA tools, even more than on Android market and ARM CPU cores. They amount of money and the number of technical experts necessary to develop an equivalent of Synopsys IC compiler is much larger, in my opinion, than the resources needed to design a high-end competitor for ARM cores.

На выставке сидел и представитель Huawei с выражением светлой печали на лице. Замечу, что если американское правительство заставит американские EDA компании банить китайцев, то китайская ситуация будет гораздо хуже, чем сейчас, так как клонировать Synopsys IC Compiler технически сложнее, чем процессорные ядра ARM и Android Market.

Every DAC since 1998 had at least one company developing yet another C-to-Verilog compiler. Back in 1998 it was my own startup. This year it is somebody else:

На каждой выствке DAC c 1998 года была по крайней мере одна компания, которая компилирует C в Verilog. В 1998 году такой компанией был мой собственный стартап. В этом году кто-то другой:

This gentleman earns his living by selling solutions that counter so-called «Zakladki» (a Russian term, a plural of «Zakladka»). I explained to him the meaning of the term and he agreed that this is what he sells.

Вот товарищ зарабатывает на жизнь анализаторами закладок в процессоры:

I brought to DAC my student daughter so she can see how daddy earns living:

В Лас-Вегас я привез свою дочь, чтобы она посмотрела, как в суровом индустриальном мире электронной промышленности люди зарабатывают деньги, и поняла, что папины доллары не на деревьях ростут:

Party after the exhibition:

На парти после выставки:

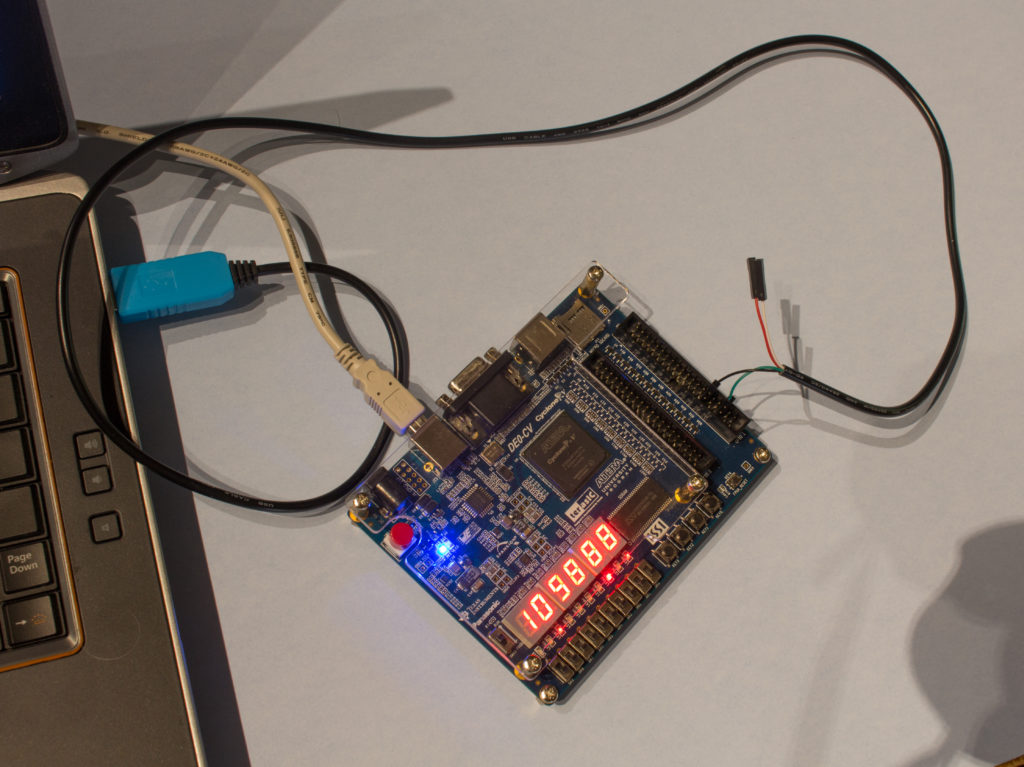

After the exhibition I did MIPS Open Developer Day together with my colleagues from Wave Comnputing. We got a number of people from some of the above companies + my Russian friends from VivEng, a California Silicon Valley mixed-signal design services that also had some customers in Zelenograd, a Russian Silicon Valley. First we made a presentation, then the participants did some exercises on Digilent Nexys4 DDR and Terasic DE10-Lite FPGA boards.

Потом я вместе с коллегами проводили семинар MIPS Open. На него пришли товарищи из некоторых описанных компаний, в том числе тех, которые лицензируют встроенные FPGA и EDA тулы, продают сервисы для производства, проводят трейнинги по верификации, а также делают чипы как таковые. А также мои старые знакомые из русской компании VivEng. Мы с коллегами показывали вот такие слайды, после чего участники пробовали примеры на FPGA платах Digilent Nexys4 DDR и Terasic DE10-Lite.

Чтобы повторить результаты, вы можете скачать и скомбинировать два пакета:

If you want to reproduce the results, you can do the following:

- Go to https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide.

- Download the standard MIPSfpga 2.0 package.

- Go to https://github.com/MIPSfpga/mipsfpga-plus.

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- Copy core RTL files from MIPS Open FPGA package to core subdirectory of MIPSfpga+ package — see the instruction in https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

На вашем компьютере должен быть установлен или Intel FPGA Quartus Prime Lite Edition, или Xilinx Vivado, а также Codescape GCC Bare Metal Toolchain. После этого вы можете следовать инструкциям со слайдов:

You need to have Intel FPGA Quartus Prime Lite Edition or Xilinx Vivado installed on your system, as well as Codescape GCC Bare Metal Toolchain. After this you can follow the instruction from the slides:

- cd your_git_directory/boards/board_directory (for example de10_lite or nexys4_ddr)

- make all load

- Press reset (or KEY 0 on some boards) to reset the processor.

- The default hardcoded program should start to work.

- cd your_git_directory/programs/00_counter (or other program)

- make program srecord uart

- If computer uses serial connection other than ttyUSB0 (the default), then:

- make program srecord uart UART=1 (or 2, 3, etc)

- The program uploaded via USB-to-UART is now running.

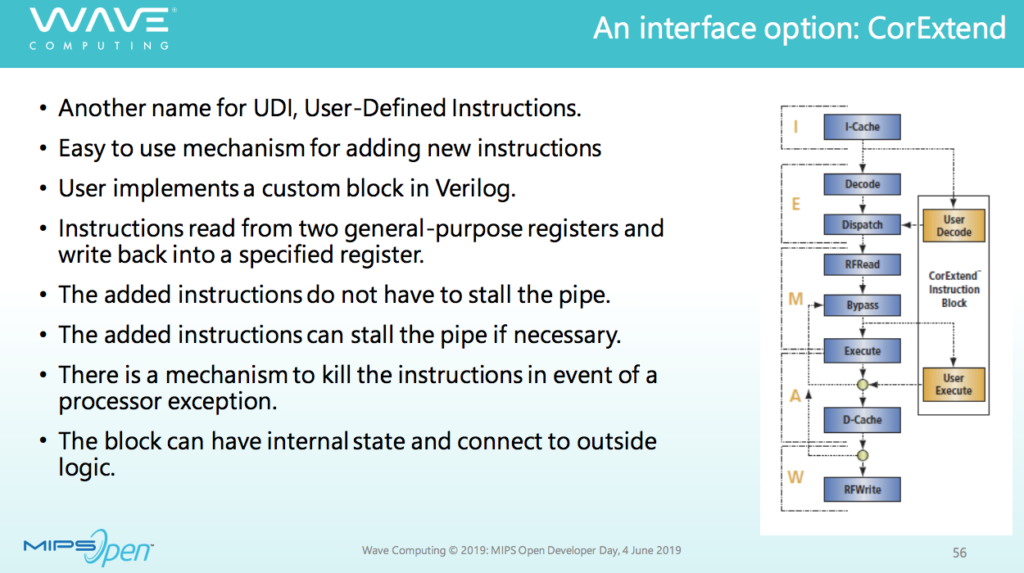

В презентации я показывал, как встроить в процессор блок, который декодирует и выполняет дополнительные к основной системе команд инструкции, которые может определить разработчик системы на кристалле. Блок может быть синтезирован и стать частью микросхемы или быть сконфигурирован в ПЛИС/FPGA.

Дополнительные инструкции двигаются по конвейеру процессора вместе с основными. Они получают данные из видимых программистом регистров общего назначения и могут вернуть результат в регистр. Эти инструкции также могут сохранять в сопроцессоре некое состояние. Их можно убить исключениями, если исключение произойдет например в следующей за данной инструкцией в конвейере:

The presentation has a detailed explanation, how to add user-defined processors instructions to MIPS microAptiv UP CPU core and synthesize it together with some simple SoC for FPGA board:

Фрагмент кода на языке описания аппаратуры Verilog из текста примера. Этот код реализует, на уровне регистровых передач (Register Transfer Level — RTL), специализированную инструкцию для вычисления сверточной нейросети:

A fragment of a custom CorExtend module that implements a User-Defined Instruction (UDI) for a special case of neural net computation:

Tomorrow I am flying to Russia to help with another seminar, not for electronic and EDA professionals, but for kids interested in exploring careers in digital microelectronic design. For this trip I created a simple 2D videoprocessor integrated with MIPS Open FPGA core, as well as an example of a hardware-only (no CPU or software) game for VGA. Kids like games and I am going to use game design to teach them the basics of RTL methodology:

А в следущий понедельник 8 июля, я буду учить основам разработки цифровых схем школьников в Зеленограде.

Для него я написал примеры реализации простой спрайтовой графики на FPGA. Синтезированная из верилога схема рисует спрайты на экране VGA.

Вот работающий пример в чистом хардвере (исходники на гитхабе). Вариант морского боя, где красный спутник-торпеда охотится за вражеским синим крестом:

А вот пример на сочетании хардвера и софтвера — салют из спрайтов. Хардверная часть и софтверная часть:

Да, и я обещал выложить свои речи в Лас-Вегасе. Вот кусок:

View of the Las Vegas Strip when its getting dark but there are no crowds yet:

И вид улицы на стрипе, когда уже вечереет, но еще нет толп:

During two days in Las Vegas I did not get a chance to gamble, so I played with $1 when our plane back to San Jose was boarding in Las Vegas airport:

За все это время в Лас-Вегасе я так и не сыграл, так как то ходил по выставке и разговаривал на электронные темы, то проводил семинар. Но во время посадки в самолет я все-таки отметился, проиграл один доллар: